| 참고 자료                                       |

|---------------------------------------------|

| VHDL을 이용한 ASIC 설계 - IDEC                    |

| VHDL을 이용한 Microprocessor 설계 - IDEC          |

| I8051 프로세서 설계 - IDEC                        |

| Altera MAX+PLUS II를 사용한 디지털 시스템 설계 - 북두 출판사 |

| 디지털 시스템 설계를 위한 VHDL - IDEC                  |

| 하드웨어 엔지니어를 위한 VHDL - 그린 출판사                 |

| MAX+PLUS II Manual                          |

| Xilinx Foundation Manual                    |

| 디지털 시스템 설계 - Mano                           |

| 인터넷에서 다운 받은 문서 - 600Mega 등                  |

# 목 차

| VHDL1 VHDL의     | 기초적인 개요                                                     | - 2 -            |

|-----------------|-------------------------------------------------------------|------------------|

|                 | 출현 배경과 VHDL의 구조<br>ASIC, FPGA 용어 정리                         | - 5 -            |

| VHDL3 VHDL에     | 사용할 문법(Altera VHDL Template)                                | - 11 -           |

| VHDLA ASIC क्ष  | 어 요약                                                        | - 22 -           |

| VHDL5 VHDL의     | 기초적인 예제와 MUX STD_LOGIC                                      | - 26 -           |

| VHDL6 조금 복접     | 말한 MUX                                                      | - 30 -           |

| VHDL7 Incremen  | nt, Decrement, 비교 연산 회로                                     | - 36 -           |

| VHDL8 DFF과 la   | atch                                                        | - 39 -           |

| VHDL9 VHDL의     | 자료형과 객체형                                                    | - 49 -           |

| VHDL10 Signal과  | Variable 그리고 Constant                                       | - 57 -           |

| VHDL11 Counter  | (Up/Down, Ring, Johnson, Gray Counter)                      | - 62 -           |

|                 | 고려사항 4가지, 설계 계층구조(Design hiera<br>g and synthesis           | archy)<br>– 74 – |

| VHDL13 Adder, 9 | 연산자, 루프문, Port map                                          | - 79 -           |

|                 | tiplier, T Flipflop, 3-state buffer의 설계<br>의 설계와 Shift 레지스터 | - 89 -           |

| VHDL15 State M  | achine                                                      | - 96 -           |

| VHDL16 Package  | 와 부프로그램                                                     | - 111 -          |

| VHDL17 Clock의   | 설계                                                          | - 117 -          |

| VHDL18 7 Seame  | ent                                                         | - 121 -          |

| 중급 과정           |                                                             | - 124 -          |

# VHDL의 기초적인 개요

VHDL이 무엇이냐?

조금 방대한 질문이네요. 일단 예제로 시작합시다. 이것을 이해하기 위해서는 Background가 어느 정도 필요합니다. 전자과 3년 과정을 마쳤다면 충분히 이해할 수 있다고 생각되네요. 참고로 제가 사용하는 Tool은 Max Plus ∏입니다.

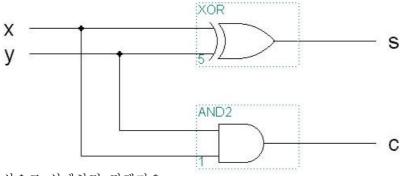

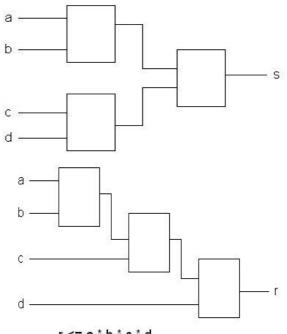

그럼 2비트 반가산기(Adder)를 설계합시다.

$$\begin{array}{l} S = x \bigoplus y \\ C = xy \end{array}$$

두 개의 입력 x, y를 입력받아 Sum, Carry를 출력합니다. 이것을 먼저 Schematic으로 구현한다고 생각합시다.

이런 식으로 설계하면 되겠지요.

그럼 이것을 VHDL로 구현해 볼까요.

-- adder2.vhd

library ieee; use ieee. std\_logic\_1164.all;

entity adder2 is

port ( x, y : in std\_logic;

s, c : out std\_logic);

architecture rtl of 2adder is begin

s <= x xor y; c <= x and y; end rtl; 조금 Language와 비슷하지요. VHDL을 회로 설계하는 언어라고 생각하면 됩니다.

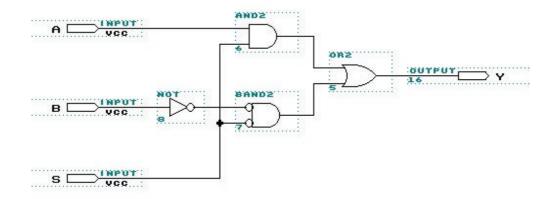

다른 2×1 MUX 예제를 봅시다. 이것을 한 번 구현해 봅시다.

이것을 VHDL로 구현해 봅시다.

-- mux21.vhd

```

library ieee;

use ieee. std_logic_1164.all;

```

entity mux21 is

port ( a, b, s : in std\_logic;

y : out std\_logic);

end mux21;

```

architecture rtl of mux21 is

begin

process(a, b, s)

begin

if ( s = '0') then

y <= a;

else

y <= b;

end if;

end process;

end rtl;</pre>

```

```

구현하는 것이 별로 어렵지는 않을 것입니다. 초보자에게는 어렵겠지만.

VHDL의 장점을 느끼지 못할 것입니다. 예제를 조금 변형해 봅시다.

입력 a, b가 4비트의 입력이라면 어떻습니까? K-map을 이용해 열심히 그려야지요.

과연 VHDL로는 어떻게 표현할 수 있을까요?

입력과 출력의 비트 수만 변형시키면 됩니다.

library ieee;

use ieee. std_logic_1164.all;

entity MUX21 is

port (a, b

: in std_logic_vector(3 downto 0);

: in std_logic;

S

y : out std_logic_vector(3 downto 0));

end MUX21;

architecture rtl of MUX21 is

begin

process(a, b, s)

begin

if (s = '0') then

v <= a;

else

v <= b;

end if;

end process;

end rtl;

```

이것이 VHDL의 장점입니다. VHDL을 이렇게 보시면 됩니다. 회로 설계를 할 수 있는 표 준 언어다. 모든 것은 장점과 단점을 가지고 있습니다. 단점에 비해 많은 장점을 가지고 있 습니다. Schematic으로 구현할 수 있는 회로는 약 5만 게이트 정도입니다. 손으로 직접 그 리는 것보다는 VHDL을 이용해 시간과 비용을 줄이는 것이 좋겠지요.

외국 검색 사이트(야후 또는 알타비스타 등등)를 이용해 VHDL을 입력해서 한번 찾아보세 요. 얼마나 많은 사이트가 존재하는지. 국내 사이트도 많이 존재하고 있습니다.

새로운 것을 배운다는 것은 힘들지만, 시간이 있는 전자가 3, 4학년에게는 적극 권하고 싶 네요. 현실적으로도 펜티엄칩도 이 VHDL을 이용해 설계하고 있습니다. 고급의 반도체 설계 나 회로 설계를 원한다면 제 강의가 아니라도 다른 책을 이용해 한번 시도해 보시기를 바랍 니다.

# VHDL의 출현 배경과 VHDL의 구조 VHDL, ASIC, FPGA 용어 정리

" VHDL의 출현 배경 및 변화 과정

미국 정부의 VHSIC Program의 주요 목적은 설계, 공정 및 제조 기술 분야에 있어서 미 국의 기술 수준을 향상시키는 데 있었다. 또한 미국 정부는 이 Program의 일부로써 VHDL 의 개발 노력을 지원하고 있었다. 그 지원 목적은 VHDL의 개발로 좀더 빠른 생산과 회 사들간의 연락 기능 강화 및 개발 과정을 능률적으로 처리함으로써 비용 절감 효과를 제공 하는 것이었다. 이러한 목적들을 효과적으로 달성할 수 있는 방법을 논의하기 위하여 메사 추세츠의 Woods Hole에서 개최된 학술 대회를 시발점으로 1981년부터 VHDL이 개발되기 시작하였다. Technology independent(기술 독립적)하며 표준 하드웨어 기술 언어의 개발을 목표로 한 Woods Hole 학술 대회에서 정부의 공식적인 제안 요구서를 위한 초안이 제출되 었으며, 이것은 전자 공학 분야에 종사하는 전문가들에 의해서 검토되는 과정을 거쳐 1983 년 초에 수정, 확정되었다. 1980년대 중반 이후부터 VHDL이 문서용이 아닌 Simulation용으 로 검증되어져야 한다는 여론이 강해지면서 몇몇 VHDL Simulator가 등장하였으나 업체간 에 표준화가 이루어지지 않은 관계로 호환성에 문제가 있었다. 이러한 문제를 해결하고 늘 어가는 VHDL관련 CAD Tool 회사간의 표준 및 호환성을 위하여 IEEE에서 1987년에 IEEE-1076이라는 표준을 만들어 공포하였다. 이 시점에서 Synthesis(회로 합성)는 아직 등 장하지 않았으며 VHDL은 Simulation용으로 사용되었다. 1990년대에 들어서면서 VHDL 관련 Software 회사가 많이 등장하고 simulation뿐만 아니라 Synthesis의 기능을 갖춘 CAD Tool이 등장하면서 진정한 VHDL의 표준화가 요구되었고 1991년 IEEE-1164가 발표되면서 업체에서 공통으로 사용할 수 있는 VHDL이 탄생하였다.

1. VHDL 이란 ?

VHDL (VHSIC (Very High Speed Integrated Circuits) Hardware Description Language) 은 상위의 동작 레벨에서부터 하위의 게이트 레벨까지 하드웨어를 기술하고 설계하도록 하는 CAD업계 및 IEEE 표준 언어이며 미국 정부가 지원을 공인한 하드웨어 설계 언어이다.

VHDL의 등장은 갈수록 복잡해지고 고집적화 되는 회로에 비례하여 어려워지는 하드웨어 설계 환경에 새로운 장을 여는 계기가 되었다. 컴퓨터 기술의 발달과 함께 VHDL을 이용한 설계 기법의 발달은 비단 이 분야에 전공하는 사람뿐만 아니라 초보자에게도 보다 쉽게 회로를 설계할 수 있는 기회를 제공하고 있다.

현재 VHDL은 세계적으로 사용되고 있으며 산업체, 대학, 연구소 등에서 그 관심이 급격히 증가하고 있다.

2. ASIC 이란

많은 사람들이 알고 있는 말 중에 하나인 ASIC이란 Application Specific IC의 약자로 우리말로 옮기게 되면 특정용도 주문형 반도체이다. 이 ASIC이란 광범위하게는 특정용도 목적으로 사용되는 모든 반도체를 가리키기도 하지만 좁게는 특히 Gate Array를 가리키는 말이다. 우리가 흔히 ASIC이라 부르며 알고 있는 상식은 Gate Array, Embedded Array, Standard Cell (또는 Cell Based IC) 세 종류를 가리키는 말로 알고 있다.

ASIC - Programmable IC Type : PAL, SOLD, COLD, PGA

- Memory IC Type: MICOM, ASIC Memory, FIFO

- Logic Based IC Type: Gate Array, Embedded Array,

Standard Cell, Full-Custom IC.

하지만 ASIC이란 반도체 회사에 제품 의뢰를 하는 Gate Array 종류만을 가리키는 것이 아닌 특정 용도나 주문형 IC모두를 다 포함하고 있다. 위에서 보는 바와 같이 ASIC의 두 가지 동류로서의 Full Custom(완전 설계 방식)과 Semi Custom(반주문형 설계 방식)이라는 말은 일본에서 인위적으로 만들어 낸 것이다. 물론 ASIC에 대하여 정확하게 정의된 것이 없는 관계로 어쩌면 Gate Array 종류를 진짜 ASIC으로 부는 것도 옳다고 할 수도 있다. 어쨌거나 일반적으로 반도체 설계를 할 수 있는 방식은 일반인들이 ASIC이라 부르고 있는 Logic Based IC Type형태의 Gate Array와 Standard Cell, 그리고 Programmable IC Type형태의 EPLD, FPGA가 대표적이다.

3. FPGA

FPGA란 Field Programmable Gate Array의 준말로 Array Based와 Row Based 두 가지 방법이 있으며 구조는 Gate Array와 매우 흡사하지만 Program에 의해 내부 회로 배선이 연결되는 형식을 취하고 있다.

FPGA는 Logic Cell 위주의 설계 방식이기 때문에 SPLD Block 내부의 배선이 외부와 직접 연결될 수 있도록 고안되어 있어 일반 Gate Array와 매우 비슷하며 Timing Simulation이 반드시 필요하다.

다른 Programmable Device에 비해 속도가 월등히 뛰어나고 집적도가 좋으며 부품 단가도 훨씬 저렴하지만 이 종류는 단 한번밖에 구울 수 없기 때문이 주로 연구 개발용보다는 제품 생산용으로 많이 사용된다.

FPGA는 대개 2,000-20,000 Gates 급의 회로에 적당하며 JEDEC을 이용하여 굽도록 되어 있는 일반 PLD 종류에 비해 Programming 하는 File이 제품을 만든 회사의 고유 Programming Netlist인 ADL, QDF, XNF 등을 사용하도록 되어 있다. Array Based 형식의 FPGA는 SPLD Block들을 2차원 배열 형식으로 늘어뜨린 다음 중간에 Interconnect Channel이 서로 교차하며 연결될 수 있도록 되어 있다. 이 Array Based형식의 FPGA는 그림에서 보는 바와 같이 두 가지 종류가 있다. 대체로 MUX와 AND로 이루어진 Combinational Logic과 하나의 Flip-Flop으로 구성되어 있는 형식의 SPLD Block구조가 일반적이며 MUX들을 일렬로 배열한 다음 중간 중간에 Flip-Flip을 끼워 넣는 형식의 Logic Array형 제품도 있다. 일반적인 내부 구조는 Xilinx의 CLB, Cypress와 QuickLogic의 Logic Cell 등이 대표적인 이 형식을 취하고 있으며 Logic Array형의 내부 구조는 Altra의 LAB가 이러한 형식을 취하고 있다.

반면 Row Based FPGA의 내부 구조는 MUX 구조 형식의 Combinational Logic이 각 행마다 나열되어 있고 중간 중간에 Flip-Flop이 끼워져 있는 형식을 취하고 있다. Array Based FPGA의 SPLD Block은 Logic Array 구조 형식이 가로가 아닌 세로로 된

Array Based FPGA의 SPLD Block는 Logic Array 구조 영식이 가도가 아닌 제도도 된 것과 비슷하다.

다만 Array Base FPGA와의 다른 점이라면 Logic Cell끼리 연결할 수 있는 Interconnect가 나열된 Cell의 아래나 위에만 위치하여야 된다는 것이다. Actel이 이 Row Based FPGA의 대표적인 구조이다.

-- 어느 인터넷 사이트에서(어딘지는 기억이 나지 않네요.)

많은 용어들이 나오죠. 나중에 용어별로 정리해 올리겠습니다. 그리고 저에게 툴 사용법을 질문하지는 마세요. 그리고 질문은 저에게보다는 모든 사람이 볼 수 있는 곳에 질문하세요. 그리고 저는 VHDL만 알고 있습니다. 혹시 verilog을 아시는 분은 verilog로 소스를 좀 올려 주시면 감사하겠습니다. verilog 역시 하드웨어 표준 언어입니다.

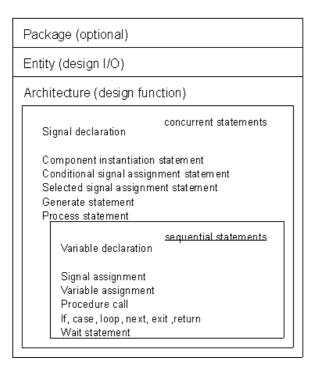

제일 먼저 살펴보아야 할 것은 VHDL의 구조입니다. VHDL이 어떤 구조로 되어 있는지 밑 에 있는 그림을 보면서 이해합시다.

영어로 되어 있으니 조금 복잡해 보이죠. 그러나 한정된 형식을 가지고 있으므로 그렇게 어렵지는 않습니다. 조금 하다 보면 자연스럽게 이해가 될 것입니다. 처음부터 모든 것을 다 이해하려고 하지 마세요.

Configuration

Package Package Body Entity Architecture

```

간단하게 표현하면 위의 5가지로 구성되어 있습니다.

지금 간단하게만 설명하고 될 수 있는 데로 예제를 중심으로 설명하는 방식을 사용하겠습니

다.

library ieee;

use ieee. std_logic_1164.all;

entity mux21 is

port ( a, b : in std_logic_vector(3 downto 0);

s : in std_logic;

y : out std_logic;

end mux21;

```

```

architecture rtl of mux21 is

begin

process(a, b, s)

begin

if ( s = '0') then

y <= a;

else

y <= b;

end if;

end process;

</pre>

```

end rtl;

```

지난 시간 설명한 MUX21의 예제다.

여기서 진하게 마크된 것은 Reserved word(예약어)이다. 이는 VHDL 구문을 사용하면서 반

드시 지켜야 할 사항이다.

```

library ieee; use ieee. std\_logic\_1164.all;

여기가 Package 부분이다. VHDL에서는 사용할 라이브러리는 LIBRARY 키워드를 이용하 여 지정해 주는데 다음과 같다.

# LIBRARY ieee;

실제로 이 라이브러리가 존재하는 디렉토리는 시뮬레이션 또는 합성툴의 환경 변수로 지정 되어 있게 된다. Compass Tool의 경우 Manager 윈도우를 띄우면 라이브러리 패스 (library path)를 지정하는 것을 볼 수 있을 것이다. MaxPlus 에도 User Library를 지정하는 메뉴가 있고 V-System/VHDL 에도 역시 라이브러리 패스를 지정하는 메뉴가 있습니다. 대개 라이 브러리 이름과 디렉토리 패스를 연결시키도록 되어 있는데, 라이브러리 명(library name)과 패스(directory path)를 맵핑(mapping) 시킨다고 한다.

USE ieee. std\_logic\_1164.ALL;

이는 ieee라는 라이브러리에서 std\_logic\_1164 라는 이름의 패키지(package)를 가져다가 그 안에 있는 함수(function)들을 모두 사용한다는 뜻으로 ALL 이라고 한 것이다. ALL은 VHDL 의 키워드이다. 물론 ALL 대신 패키지 내에서 사용할 함수를 지정할 수도 있다.

사용툴의 Library 디렉토리에 가면 ieee. vhd 라는 파일이 있다. 이것을 직접 확인해 보는 것도 좋은 방법이다. 각각의 툴마다 조금씩 차이가 나는 것을 알 수 있을 것이다.

entity mux21 is

port ( a, b : in std\_logic\_vector(3 downto 0);

s : in std\_logic;

y : **out** std\_logic\_vector(3 downto 0));

end mux21;

시스템을 구성하는 부분품으로서 이들 사이의 상호 연결을 위한 통로 역할(interface)을 하는 것이 Entity이다. 말하자면 내부 설계에 대한 입출력 등을 기술하는 "포장"인 셈이다. 시스템의 입장에서 보면 내부 설계에 대한 것은 가려져 있고 다만 ENTITY에 기술된 입출 력 포트만을 보게 되는데 이런 의미에서 ENTITY를 "암흑 상자"(Black Box)라고 하기도 한다.

위의 예제에서 보면 Entity name은 MUX21이고 각종 포트에 대한 설명을 한다. <u>몇몇의 툴</u> 에서는 Entity name과 파일의 이름이 일치해야 하는 경우도 있으니 참조하기 바란다(Max Plus Ⅱ의 경우), 입력과 출력에 대한 포트의 설명이다.

포트 name은 Reserved word와 일치해서는 안 된다.(중요)

in, out 이라고 한 것이 입력과 출력의 표시이다. in은 입력을 나타내고 out은 출력을 나 타낸다. 그 외에도 buffer 모드와 inout 모드가 있다. 다음에 예제를 통해 설명하겠지만 지 금 간단히 설명하면 다음과 같다. INOUT은 입출력 포트로 사용되므로 소스(source) 또는 목적지(destination)에 모두 쓸 수 있다. 그러나 한 개의 문장에 모두 쓸 수 없다. 입출력 모 드가 정해진 경우 할당문(assign statement)에서의 엄격한 규정은 하드웨어를 다루기 때문 이다. 하드웨어를 기술할 때 assign 이란 연결 관계를 표현한 것(netlist)으로서 프로그래밍 언어에서와 같은 오퍼레이션(move operation)이 아니다. BUFFER는 INOUT과 같은 입출력 포트로서 assign의 소스(source)측 또는 목적지(destination)측에 쓸 수 있다. INOUT 모드와 다른 점은 단일 할당문 내에서 소스와 목적지측 모두 동시에 사용할 수 있다는 것이다. 이 는 BUFFER 모드에 이미 F/F를 내포하고 있다는 의미를 갖는다.

1비트의 경우는 std\_logic으로 표현하고, 다중 비트의 경우는 std\_logic\_vector(n downto 0) 라고 표현한다.

std\_logic\_vector(0 to 3)

std\_logic\_vector(3 downto 0)

위의 두 가지 모두 MSB가 왼쪽에 있는 4비트를 표현한 것이다.

std\_logic 이외에도 객체형(Object Types)이 있지만 뒤에 설명하는 것이 좋겠다.

한가지 양해를 구할 것이 있다. 설계를 하다 보면 그 정식 용어를 써야 할 때가 많다. 그 래서 되도록 원문을 사용하는 것이 좋다고 판단된다. 그래서 영어가 나와도 그대로 받아들 이기를 원한다. 현 추세의 하드웨어 설계는 혼자서 하는 것이 아니다. 아직 Configure에 대 한 설명은 하지 않았지만 Configure의 역할은 여러 사람의 설계를 조합할 때 사용하는 것이 다. Pentinum 설계에 투입된 인원이 600명 이상이라고 한다. 그만큼 현 추세는 복잡하고 세 분화되어 있다. 뒷부분에서 Configure의 자세한 부분들 다루기로 하겠다. 지금은 예제가 간 단하므로 Configure의 설정이 필요하지 않다.

```

architecture rtl of mux21 is

begin

process(a, b, s)

begin

if ( s = '0') then

y <= a;

else

y <= b;

end if;

end process;

ond rtl;</pre>

```

end rtl;

다음은 architecture 부분이다.

아직 버그가 잡혔는지는 모르겠지만, Lodecap에서는 architecture name과 entity name이 같 아야 하는 이상한 버그가 있었다. (지금은 해결되었을 것이라 판단된다.) architecture name 과 entity name을 다르게 잡아 주는 것이 좋다고 생각된다. architecture name과 entity name을 정할 때 그 파일이 어떤 파일인지 자기가 구별할 수 있도록 하는 습관은 좋은 습관 이다. 모든 architecture에서는 Concurrent(동시에 수행)하게 동작된다. 모든 하드웨어 설계 의 기본의 동작이 Concurrent하게 발생된다. Sequential(순차적으로)하게 표현하기 위해서 Process 문을 사용한다. Process 문안에서의 모든 동작은 순차적으로 발생된다. 하나의 Architecture 안에 다수의 Process 문을 사용할 수 있다. 그리고 적어도 하나 이상의 Entity와 Architecture 문을 구성할 수 있다.

다음에는 많은 예제를 가지고 VHDL의 표현에 대해서 예제를 중심으로 설명하겠습니다. 많은 예제를 가지고 그것을 시뮬레이션 하다 보면 자연스럽게 VHDL의 문법을 익힐 수 있 을 것입니다.

# VHDL에 사용할 문법(Altera VHDL Template)

# 1. Overall Structure

- -- Context Clauses

- -- Library Clause

- -- Use Clause

# -- Library Units

- -- Package Declaration (optional)

- -- Package Body (optional)

- -- Entity Declaration

- -- Architecture Body

# 2. Full Design : Counter

-- MAX+plus II VHDL Template

-- Clearable loadable enablable counter ENTITY \_\_entity\_name IS PORT ( INTEGER RANGE 0 TO \_\_count\_value; \_\_\_data\_input\_name : IN \_\_clk\_input\_name : IN STD\_LOGIC; STD\_LOGIC; \_\_clrn\_input\_name : IN STD\_LOGIC; \_\_ena\_input\_name : IN \_\_ld\_input\_name : IN STD\_LOGIC; \_\_\_count\_output\_name : OUT INTEGER RANGE 0 TO \_\_count\_value ); END \_\_\_entity\_name; ARCHITECTURE a OF \_\_entity\_name IS SIGNAL \_\_count\_signal\_name : INTEGER RANGE 0 TO \_\_count\_value; BEGIN PROCESS (\_\_clk\_input\_name, \_\_clrn\_input\_name) BEGIN IF \_\_clrn\_input\_name = '0' THEN \_\_count\_signal\_name <= 0;</pre> ELSIF (\_\_clk\_input\_name' EVENT AND \_\_clk\_input\_name = '1') THEN IF \_\_ld\_input\_name = '1' THEN \_\_count\_signal\_name <= \_\_data\_input\_name;</pre> ELSE IF \_\_\_ena\_input\_name = '1' THEN ount\_signal\_name <= \_\_count\_signal\_name + 1;</pre> ELSE \_\_count\_signal\_name <= \_\_count\_signal\_name;</pre> END IF; END IF; END IF; END PROCESS; \_\_count\_output\_name <= \_\_count\_signal\_name;</pre> END a;

```

3. Full Design : Flipflop

-- MAX+plus II VHDL Template

-- Clearable flipflop with enable

LIBRARY ieee;

USE ieee. std_logic_1164.all;

ENTITY __entity_name IS

PORT

(

STD_LOGIC;

___d_input_name

: IN

__clk_input_name : IN

STD_LOGIC;

STD_LOGIC;

__clrn_input_name : IN

STD_LOGIC;

__ena_input_name : IN

: OUT STD_LOGIC

__q_output_name

);

END ___entity_name;

ARCHITECTURE a OF __entity_name IS

SIGNAL __q_signal_name : STD_LOGIC;

BEGIN

PROCESS (__clk_input_name, __clrn_input_name)

BEGIN

IF __clrn_input_name = '0' THEN

__q_signal_name <= '0';

ELSIF (__clk_input_name' EVENT AND __clk_input_name = '1') THEN

IF __ena_input_name = '1' THEN

__q_signal_name <= __d_input_name;

ELSE

__q_signal_name <= __q_signal_name;

END IF;

END IF;

END PROCESS;

__q_output_name <= __q_signal_name;

END a;

```

- 13 -

```

4. Full Design : Tri-State Buffer

-- MAX+plus II VHDL Template

-- Tri-State Buffer

LIBRARY ieee;

USE ieee. std_logic_1164.all;

ENTITY __entity_name IS

PORT

(

__oe_input_name

: IN

STD_LOGIC;

__data_input_name

: IN

STD_LOGIC;

__tri_output_name

: OUT

STD_LOGIC

);

END ___entity_name;

ARCHITECTURE a OF __entity_name IS

BEGIN

PROCESS (__oe_input_name, __data_input_name)

BEGIN

IF __oe_input_name = '0' THEN

__tri_output_name <= 'Z';</pre>

ELSE

__tri_output_name <= __data_input_name;</pre>

END IF;

END PROCESS;

END a;

```

# 5. Architecture Body

# 6. Case Statement

```

CASE __expression IS

WHEN __constant_value =>

__statement;

___statement;

WHEN __constant_value =>

___statement;

__statement;

WHEN OTHERS =>

___statement;

___statement;

END CASE;

7. Component Declaration

COMPONENT __component_name

PORT(

__input_name, __input_name

: IN

```

| bidir_name,bidir_name   | : INOU'I | STD_LOGIC;  |

|-------------------------|----------|-------------|

| output_name,output_name | : OUT    | STD_LOGIC); |

| END COMPONENT;          |          |             |

STD\_LOGIC;

# 8. Component Instantiation Statement

\_\_instance\_name: \_\_component\_name PORT MAP ( \_\_formal\_parameter => \_\_actual\_parameter, \_\_formal\_parameter => \_\_actual\_parameter);

# 9. Concurrent Procedure Call

\_\_label: \_\_procedure\_name(\_\_actual\_parameter, \_\_actual\_parameter);

# 10. Concurrent Signal Assignment Statement

\_\_signal <= \_\_expression;

#### 11. Conditional Signal Assignment

\_\_label: \_\_signal <= \_\_expression WHEN \_\_boolean\_expression ELSE \_\_expression WHEN \_\_boolean\_expression ELSE \_\_expression;

# 12. Constant Declaration

CONSTANT \_\_constant\_name : \_\_type\_name := \_\_constant\_value;

# 13. Entity Declaration

# ENTITY \_\_entity\_name IS PORT( \_\_input\_name, \_\_input\_name : IN STD\_LOGIC; \_\_input\_vector\_name : IN STD\_LOGIC\_VECTOR(\_\_high downto \_\_low); \_\_bidir\_name, \_\_bidir\_name : INOUT STD\_LOGIC; \_\_output\_name, \_\_output\_name : OUT STD\_LOGIC); END \_\_entity\_name;

# 14. For Statement

\_loop\_label:

FOR \_\_index\_variable IN \_\_range LOOP

\_\_statement;

\_\_statement;

END LOOP \_\_loop\_label;

# 15. Generate Statement ( For Statement)

\_\_generate\_label: FOR \_\_index\_variable IN \_\_range GENERATE \_\_statement; \_\_statement; END GENERATE;

# 16. Generate Statement ( If Statement)

\_\_generate\_label: IF \_\_expression GENERATE \_\_statement; \_\_statement; END GENERATE;

# 17. If Statement

```

IF __expression THEN

__statement;

__statement;

ELSIF __expression THEN

__statement;

__statement;

ELSE

__statement;

END IF;

```

# 18. Library Clause

LIBRARY \_\_library\_name;

#### 19. Package Declaration

PACKAGE \_\_package\_name IS

- -- Type Declaration

- -- Subtype Declaration

- -- Constant Declaration

- -- Signal Declaration

- -- Component Declaration

- END \_\_package\_name;

# 20. Procedure Call Statement

\_\_procedure\_name(\_\_actual\_parameter, \_\_actual\_parameter);

# 21. Process (Combinatorial Logic)

\_\_process\_label:

PROCESS (\_\_signal\_name, \_\_signal\_name, \_\_signal\_name) VARIABLE \_\_variable\_name : STD\_LOGIC; VARIABLE \_\_variable\_name : STD\_LOGIC;

BEGIN

- -- Signal Assignment Statement

- -- Variable Assignment Statement

- -- Procedure Call Statement

- -- If Statement

- -- Case Statement

- -- Loop Statement

END PROCESS \_\_process\_label;

# 22. Process (Sequential Logic)

\_\_process\_label:

PROCESS VARIABLE \_\_variable\_name : STD\_LOGIC; VARIABLE \_\_variable\_name : STD\_LOGIC;

BEGIN

WAIT UNTIL \_\_clk\_signal = '1';

- -- Signal Assignment Statement

- -- Variable Assignment Statement

- -- Procedure Call Statement

- -- If Statement

- -- Case Statement

- -- Loop Statement

END PROCESS \_\_process\_label;

# 23. Selected Signal Assignment Statement

#### \_label:

```

WITH __expression SELECT

__signal <= __expression WHEN __constant_value,

__expression WHEN __constant_value,

__expression WHEN __constant_value;

__expression WHEN __constant_value;

```

#### 24. Signal Declaration

SIGNAL \_\_signal\_name : \_\_type\_name;

# 25. Signal Assignment Statement

\_\_signal\_name <= \_\_expression;</pre>

# 26. State Machine with Async. Reset

ENTITY \_\_machine\_name IS PORT( : IN STD\_LOGIC; clk : IN STD\_LOGIC; reset : IN STD\_LOGIC; \_\_input\_name, \_\_input\_name \_\_output\_name, \_\_output\_name : OUT STD\_LOGIC); END \_\_machine\_name; ARCHITECTURE a OF \_\_machine\_name IS TYPE STATE\_TYPE IS (\_\_state\_name, \_\_state\_name, \_\_state\_name); SIGNAL state: STATE\_TYPE; BEGIN PROCESS (clk) BEGIN IF reset = '1' THEN state <= \_state\_name;</pre> ELSIF clk' EVENT AND clk = '1' THEN CASE state IS WHEN \_\_state\_name => IF \_\_condition THEN state <= \_\_state\_name;</pre> END IF; WHEN \_\_state\_name => IF \_\_condition THEN state <= \_\_state\_name;</pre> END IF; WHEN \_\_\_state\_name => IF \_\_condition THEN state <= \_\_state\_name;</pre> END IF; END CASE; END IF; END PROCESS; WITH state SELECT \_\_output\_value \_\_state\_name, WHEN \_\_output\_name <= \_\_output\_value WHEN \_\_\_state\_name, WHEN \_\_output\_value \_\_\_state\_name;

END a;

# 27. State Machine without Async. Reset

| ENTITY | machine_name IS                |                  |           |            |             |

|--------|--------------------------------|------------------|-----------|------------|-------------|

|        | PORT(                          |                  |           |            |             |

|        | clk                            |                  | : IN      | STD_LC     | )GIC;       |

|        | input_name,input_nam           | e                | : IN      | STD_LC     | )GIC;       |

|        | output_name,output_na          | ame              | : OUT     | STD_LC     | )GIC);      |

| END _1 | nachine_name;                  |                  |           |            |             |

|        |                                |                  |           |            |             |

| ARCHIT | ECTURE a OFmachine_name IS     |                  |           |            |             |

|        | TYPE STATE_TYPE IS (state_name | me, <u>state</u> | _name, _  | _state_nar | ne);        |

|        | SIGNAL state: STATE_TYPE;      |                  |           |            |             |

| BEGIN  |                                |                  |           |            |             |

|        | PROCESS (clk)                  |                  |           |            |             |

|        | BEGIN                          |                  |           |            |             |

|        | IF clk' EVENT AND clk =        | '1' THEN         |           |            |             |

|        | CASE state IS                  |                  |           |            |             |

|        | WHEN                           | state_nan        | ne =>     |            |             |

|        |                                | IFcond           |           | IEN        |             |

|        |                                |                  | state <=  | state_     | name;       |

|        |                                | END IF;          |           |            |             |

|        | WHEN                           | state_nan        | ne =>     |            |             |

|        |                                | IFcond           | lition TH | IEN        |             |

|        |                                |                  | state <=  | =state_    | name;       |

|        |                                | END IF;          |           |            |             |

|        | WHEN                           | state_nan        | ne =>     |            |             |

|        |                                | IFcond           | lition TH | IEN        |             |

|        |                                |                  | state <=  | state_     | name;       |

|        |                                | END IF;          |           |            |             |

|        | END CASE;                      |                  |           |            |             |

|        | END IF;                        |                  |           |            |             |

|        | END PROCESS;                   |                  |           |            |             |

|        |                                |                  |           |            |             |

|        | WITH state SELECT              |                  |           |            |             |

|        | output_name <=                 | output_          |           |            | state_name, |

|        |                                | output_          |           |            |             |

|        |                                | output_          | value     | WHEN       | state_name; |

END a;

28. Subtype

SUBTYPE \_\_subtype\_name IS \_\_type\_name RANGE \_\_low\_value TO \_\_high\_value; SUBTYPE \_\_array\_subtype\_name IS \_\_array\_type\_name(\_\_high\_index DOWNTO \_\_low\_index);

# 29. Type

TYPE \_\_enumerated\_type\_name IS (\_\_name, \_\_name, \_\_name); TYPE \_\_range\_type\_name IS RANGE \_\_integer TO \_\_integer; TYPE \_\_array\_type\_name IS ARRAY (INTEGER RANGE <>) OF \_\_type\_name; TYPE \_\_array\_type\_name IS ARRAY (\_\_integer DOWNTO \_\_integer) OF \_\_type\_name;

30. Use Clause

USE \_\_library\_name.\_\_package\_name. ALL;

# 31. Wait Statement

WAIT UNTIL \_\_clk\_name = '1';

#### 32. Variable Declaration Statement

VARIABLE \_\_variable\_name : \_\_type\_name;

#### 33. Variable Assignment Statement

\_\_variable\_name := \_\_expression;

# 34. While Statement

\_loop\_label: WHILE \_\_boolean\_expression LOOP \_\_statement; \_\_statement; END LOOP \_\_loop\_label;

위에 있는 것들은 VHDL에 사용할 문법들입니다. 이것은 Altera의 문법들입니다. VHDL이 하드웨어 표준 언어이지만 각 회사들마다 조금씩 문법의 차이는 있습니다. 실 예로 Lodecap 에서 모든 컴파일과 시뮬레이션을 마친 상태에서 그 소스를 Altera에서 실행한 적이 있습니 다. 그런데 상태 이름이 Next였습니다. 그런데 MaxPlus II에서는 Next가 Reserved word이 었습니다. 그래서 몇 일을 고생한 적이 있습니다. 자기가 사용하는 툴에 대해서는 어느 정도 의 지식이 있어야 합니다.

그러니 각 회사 사이트에 접속하면 Manual을 구할 수 있습니다. 그리고 공개용 버전도 어 느 정도 구할 수 있을 것입니다. 직접 접속해 보시는 것도 좋은 방법입니다.

# ASIC 용어 요약

1 ASIC : Application Specific Integrated Circuit 주문형 반도체 시스템 업체가 자기 시스템의 특정 회로 부분을 하나의 반도체로 집적시켜 개발하여. 반도체 제조업자에게 주문 제조한 반도체 수요 업체가 주문 제조한 특정 회로용으로만 사용되기 때문에 기존의 범용 반도체(반도체 업체가 생산하는 표준화된 반도체:Standard IC )와 상대적인 개념으로 특정용도 IC(ASIC)라 통칭함. 2 ATVG : Automatic Test Vector Generation 일반적으로 결점 적용 범위(Fault Simulation)의 레벨을 증가시키고, 기능을 검사하기 위한 테스트 패턴 (Test Pattern)들을 증가시키기 위해 이용된다. 3 Back Annotation 레이아웃(Layout)후에 R. C값을 추출하는 작업 4 Behavioral Description 알고리즘 또는 수학적인 방정식의 항으로부터 소자 또는 기능을 모델화하는것. 5 Bottom-up Design 계층적 설계 방법 (Hierarchical Design)을 이용하여 트랜지스터나 게이트 같은 기본적인 소자로부터 셀(cell),모듈(module)등 중간 레벨의 구조를 만들고 정의하여, 높은 레벨의 시스템 구조를 꾸며 나가는 설계 방식(Top-Down Design과 상대적 개념) 2.6 Cell 특정한 전기적 기능을 수행하기 위해 이미 정의된 회로 소자의 레이아웃이나 파일 7. Cell Library 특성을 가진 셀 들의 모임으로 일반적 ASIC 벤다(Vendor)회사에 특정된다. 8. CIF : Caltech Intermediate Format 표준형 기계가 읽을 수 있도록 마스크 레벨인 도형적 레이아웃을 표현하기 위한 형식. 레이아웃의 표준으로 GDSII도 있다. 9. Core I/O 패드 링 (Pad Ring)을 제외한 영역 또는 ASIC의 능동 영역 10. Critical Path 회로망에서 가장 긴 경로, 임계 경로 전달 지연은 소자의 최대 클락 주파수를 제한한다. 11. Design Rule 도형적 레이아웃을 이루는 다각형들에 대한 최소의 너비와 간격에 대한 요구 사항들을 정의한 것. 테크놀러지별로 Metall, Metal2, Poly등의 값들을 정의. 12. DFT : Design For Testability 테스트 용이화 설계(DFT)는 회로 설계단계시, 논리회로의 테스트를 손쉽게 할 테스트 패턴 생성을 고려하여 설계하는 것이다. 13. DIE 칩이라고도 부름. 다이는 회로나 소자의 어레이를 포함하는 웨이퍼를 스크라이브선 (Scribe

Line)을 따라 잘라서 얻은 하나의 집적된 회로이다.

14. DRC : Design Rule Checker 설계 아트워크가 어떤 특정 공정에서 아무런 문제없이 제작될 수 있는가를 검토하기 위하여, 완전한 레이아웃을 공간적인 면에서 공정 설계 규칙에 맞는지 검토하는 프로그램. 15. EDA : Electronic Design Automatic 컴퓨터를 이용한 회로 설계 자동화 엔지니어링 Tools에 상응함. 16. EDIF : Electronic Data Interchange Format 어떤 설계 툴에서 만들어진 데이터를 다른 설계 Tools로 전송하기 위한 표준화된 중간 서식. 17. ERC : Electronic Rule Checker 과다한 팬 아웃, 개방(Open), 단락(Short)과 같은 전기 법칙의 위반들에 대하여 회로 레이아웃을 검토하는 프로그램. 18. Fault 어떤 회로의 개방 또는 단락으로 인하여 기능적 고장을 초래하는 제조상의 결함. 19. Floating Node 연결되지 않은 채 남겨진 게이트의 입력 또는 출력으로 놓아두면 기능적 고장을 유발하게 된다. 부동 단자는 대개 논리적으로 High 상태로 부동한다. ERC 프로그램들이 이런 레이아웃 에러를 검색하는데, 이것들은 공정 중에 불안전한 접촉에 의해 발생하기도 한다. 20. Floor Planning 최적의 레이아웃을 얻기 위하여 칩 레이아웃 영역 내의 기능 블럭들을 배치하고, 그 기능 블럭들 사이를 연결하여 할당하는 과정. 21. Foundry ASIC 설계 업체와 고객들이 자신들이 갖고 있는 공정에 적합한 Function Block들을 사용. 완성된 설계를 제조하기 위하여 이용할 수 있는 반도체 제조 설비 22. Gate 두개 이상의 입력들과 하나의 출력을 가진 회로로, 출력은 입력 신호의 논리 함수로 표시된다. 기본적인 논리 게이트 형태로는 AND, OR, NAND, NOR와 같은 불렌함수(Boolean Function)들이 있다. 23. GDSII 마스크를 만들기 위한 레이아웃을 생성시키기 위하여 사용되는 설계 데이터 형식의 하나로 다른 형식으로는 CIF가 있다. 24. Hierarchical Design 하나의 모듈을 여러 종속 모듈들로 나누어 설계하는 방식으로 ,하나의 논리를 구조적으로 표기하는 방법. 예를 들면 하나의 마이크로 프로세서 블럭은 게이트 블럭 도로 구성된 플립플롭 블럭을 포학하고 이 블럭들로 구성된 하나의 프로그램 카운터 블럭을 포함하고 있다. 25. Load 구동 소자의 출력에 존재하는 저항이나 커패시턴스.

26. Macro Cell / Hard Macro 코아 기능이라고도 하는데, 매크로는 본래 표준형 카탈로그 부품으로 제공되는 어떤 기능을 수행하는 복잡한 ASIC 셀이다. 하드 매크로로 불리기도 한다. (레이아웃이 설계 규칙에 맞게 고정되어 있기 때문) 27. Maintenance 소프트웨어 회사의 툴에 대해 기술적 지원, 오류 정정 소프트웨어 개선, 서비스 등을 제공받기 위해, 사용자가 소프트웨어 회사에 지불하는 비용. 28. MPW : Multi Project Wafer 여러 다른 설계자에 의해 설계된 여러 개의 다른 프로젝트들을 한 웨이퍼 상에 제조함으로써 NRE비용을 여러 설계자들에게 분담시키는 방법. 29. Netlist 임의의 설계 구성 셀들과 이들의 연결 상태에 대한 정보 나열. 30. Net Comparison or Netcompare Schematic Capture에서 얻어진 네트리스트와 레이아웃의 네트리스트가 같은 기능과 연결성을 갖는지를 비교 검토하는 것. 31. Node 회로 요소 또는 한 회로망의 임의 가지의 단자. 32. NRE : Non Recurring Engineering ASIC 시제품 제작을 위한 개발 노력 행위와 그에 연관된 비용에 관한 것. 33. Pad I/O 회로를 패키지 또는 기판에 연결하기 위해 사용되는 칩 가장자리에 위치한 금속 영역. 34. P & R 레이아웃의 배치 및 배선 35. PGA : Pin Grid Array 어떤 그리드에 나열된 패키지의 리드(Lead)를 패키지 몸체 밑의 아래 방향으로 나오게 하는 Through Hole 장착 패키지 기술. 36. Physical Design 트랜지스터, 셀, 블럭과 그것들의 배치와 배선을 포함하는 기하학적 요소들의 항으로 집적회로 레이아웃을 도형적으로 구현하는 것. 37. Placement 칩 레이아웃 내의 세 또는 블럭들을 물리적으로 위치시키는 것. 38. Primitive 게이트와 같은 낮은 레벨의 기능. 39. Prototype 어떤 특정한 응용에 대해 첫 번째 설계 또는 첫 번째 동작 모델의 형태. 정확성과 기능을 평가하기 위한 시제품 혹은 시작품.

41. Routing Cell들 사이의 연결 통로. 42. Scribe Line 인접한 다이의 위치를 분리시키는 웨이퍼 상의 영역. 스크라이브 영역 선은 각각의 칩을 산출하기 위해 줄쳐 있거나 잘려지는 선 43. Sea of Gate 배선용 채널을 따로 가지지 않으며 트랜지스터가 연속적으로 배열된 게이트 어레이 구조의 한 형태. 44. Silicon Compiler 고수준 설계 표기가 주어졌을 때, 도형적 설계와 시뮬레이션을 포함하는 모든 필요한 설계 관점들을 컴파일 하거나 종합하는 설계 툴. 45. Simulation or Test Vector 회로의 입력에 적용되어 연산되었을 때, 도형적 설계와 시뮬레이션을 포함하는 모든 필요한 설계 관점들을 컴파일 하거나 종합하는 설계 툴. 46. Standard Cell 고정된 물리적, 전기적 특성들에 의해 특정 지어지는 게이트 또는 레치 같은 기본적인 기능적인 요소. 47. Symbol 셀의 경계 박스와 I/O 포트를 그림으로 나타낸 것. 48. Synthesis 상태 천이 기계, 진리표, 진리도는 불린 방정식 등의 고수준 설계 서술을 특정한 게이트 레벨 논리 구현으로 변환하는 것. 49. VHDL : VHSIC Hardware Description Language 언어적 사양에 따라 기능적 등가 칩을 생산할 수 있는 많은 ASIC회사들에 의해 이상적으로 선정된 사양을 만드는데 사용되는 기술도립적인 표준형 설계 표기 언어. (IEEE 1076)50. Yield 웨이퍼 상의 올바로 동작하는 칩수와 전체 칩수의 비율.

# VHDL의 기초적인 예제와 MUX STD\_LOGIC

이번 시간부터는 많은 예제를 통하여 기초적인 회로를 구현해 보도록 하겠습니다. 많은 예 제를 통해 자기 자신만의 코딩 스타일을 가지는 것도 중요한 일이지요.

| ex1)                                   | ex2)                                          |

|----------------------------------------|-----------------------------------------------|

| 논리식                                    | 논리식                                           |

| library ieee;                          | library ieee;                                 |

| use ieee. std_logic_1164.all;          | use ieee. std_logic_1164.all;                 |

|                                        |                                               |

| entity ex1 is                          | entity ex1 is                                 |

| port ( a, b, c : in bit;               | <b>port</b> ( a, b, c : in std_logic;         |

|                                        |                                               |

| z : out bit);                          | $z$ : <b>out</b> std_logic);                  |

| z : <b>out</b> bit);<br>end ex1;       | z : <b>out</b> std_logic);<br><b>end</b> ex1; |

|                                        |                                               |

|                                        |                                               |

| end ex1;                               | end ex1;                                      |

| end ex1;<br>architecture rtl of ex1 is | end ex1;<br>architecture rtl of ex1 is        |

세미콜론(;)을 붙이는 것도 상당히 중요합니다. 여기서는 두 가지의 중요한 사항이 있습니 다. 눈썰미가 있는 분들은 한가지는 찾으셨겠죠. C 언어나 다른 언어의 기초적인 사항만 알 면 별로 어려운 문법은 없다고 생각됩니다.

먼저 우리가 할 일을 먼저 생각합시다. 컴파일을 통해 일단 버그(?)를 잡아야 하겠죠. VHDL의 문법은 상당히 엄격합니다. 그래서 그 규정을 지키지 않으면 제대로 테스트하기가 어렵습니다. 컴파일이 끝나면 시뮬레이션을 통해 그 결과를 확인해야 합니다. 시뮬레이션 시 중요한 것은 Delay가 어떻게 되는지 생각해야 합니다. 결과가 제대로 나왔다고 해서 그 결 과를 만족해서는 안됩니다. 중요한 것은 Real-time Simulation을 해야 한다는 것입니다. 초기부터 항상 이것을 명심하기를 바랍니다. 시뮬레이션이 끝나면 그 결과를 구현해 보는 것도 중요합니다. 보드가 없는 사람은 시뮬레이션으로 끝나야 하겠지만 여건이 가능하다면 항상 구현해 보는 것도 즐거운 일입니다.

이 두 예제의 차이점은 bit와 std\_logic의 차이입니다. bit는 전기적인 신호 '1'과 '0'을 말 합니다. 전자 회로의 기초적인 사항이죠.

std\_logic 이란 무엇인가요? 이것을 이해하기 전에 이것을 시뮬레이션으로 구현해 보셨 나요? 결과가 어떻습니까? 같은 결과를 보여주죠.

디지털 전자 회로는 어떻습니까? '1'과 '0'으로 모든 것을 다 표현할 수 있었습니까? 그렇지 는 않죠. K-map을 배웠다면 Don't care도 배웠을 것입니다. 그리고 결과를 표시할 수 없 는 Undefined도 배웠을 것입니다. 그러니 '1'과 '0'이 모든 것을 표현할 수는 없습니다. 그래 서 IEEE에서는 표준화되어서 나온 것이 Std\_logic입니다. Std\_logic은 nine values를 가지 고 있습니다. 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

디지털 전자 회로를 표현하기 위해서는 이것이 정의되어야 합니다. 그리고 VHDL 논리 연 산으로는 AND, NAND, OR, NOR, XOR, XNOR, NOT가 있습니다. 위의 예제에서 쓰인 것 처럼 연산을 직접 하면 됩니다. 예제 처음에 '--'이라는 표시가 있지요. 이것은 C에서처럼 주석을 표시합니다. 한 문장의 끝까지 주석으로 처리합니다. 주석 입력이 한글로 되지 않는 툴이 많습니다. 심지어 한글로 된 디렉토리까지 읽지 못하는 경우도 있으니 되도록 디렉토 리나 파일명을 영어로 입력하기를 바랍니다.

다음은 Assign에 대해서 설명하겠습니다.

$z \leq (a \text{ and } b) \text{ or } c;$

입력포트로서 signal assign의 소스(source)측 (Signal일 경우 '<=', Variable일 경우 ':=' 의 오른쪽, R-Value)에만 쓸 수 있습니다. OUT은 출력포트로서 signal assign의 목적지 (destination) ('<=' 또는 ':='의 왼쪽, L-Value)에만 쓸 수 있습니다. 위 예제에서 입력은 a, b, c로 정해져 있고 출력은 z로 정해져 있습니다. 아니 우리가 그렇게 입출력을 정했죠. 지 금과 같이 입출력 모드가 정해진 경우 할당문(assign statement)에서는 엄격한 규정으로 하 드웨어를 다룹니다. 하드웨어를 기술할 때 assign이란 연결 관계를 표현한 것(netlist)으로서 프로그래밍 언어에서와 같은 오퍼레이션(move operation)과는 다른 의미입니다.

두 예제를 분석하는 데에도 상당히 장난이 아니죠.

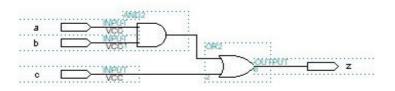

위 그림처럼 두 개의 게이트와 3개의 입력 패드 와 한 개의 출력 패드만 있으면 되는데 말 이죠.

다음 예제 3가지 모두 같은 기능을 가지는 4×1 Mux입니다. 예제 3과 4는 Concurrent하게 설계되었고 나머지 하나는 Process 문안에서 Sequential하게 설계되었습니다.

ex3)

ex4)

library ieee; use ieee. std\_logic\_1164.all;

```

entity mux41 is

port ( a, b, c, d : in std_logic;

sel          : in std_logic(1 downto 0);

y          : out std_logic);

end mux41;

```

```

architecture rtl of mux41 is

begin

y <= a when ( sel = "00" ) else

b when ( sel = "01" ) else

c when ( sel = "10" ) else

d when ( sel = "11");</pre>

```

library ieee; use ieee. std\_logic\_1164.all;

```

architecture rtl of mux41 is

begin

with sel select

y <= a when "00",

b when "01",

c when "10",

d when "11";

```

end rtl;

ex5) library ieee; use ieee. std\_logic\_1164.all;

```

end mux41;

```

end rtl;

```

architecture rtl of mux41 is

begin

process(sel, a, b, c, d)

begin

case sel is

when "00" => y <= a;

when "01" => y <= b;

when "10" => y <= c;

when others => y <= d;

end case;

end process;

end rtl;</pre>

```

예제 3, 4, 5 모두가 1-way 4 ×1 Multiplexor를 설계한 것이다. 이제부터의 예제에서는 사용되는 문법을 익히기 바란다. 예제 3, 4와 예제 5가 다른 점은 Process문이 없다는 것이다. 앞에서도 설명했듯이 Concurrent와 Sequential 문의 차이지만 기능은 같다. 여기서 자기 스 타일에 맞는 예제를 선택해 자기 자신의 코딩 스타일을 갖는 것은 중요하다. 그 전에 Delay 문제와 Gate Counter를 통해 어떤 것이 가장 잘 설계되었는지 확인하는 것이 중요하다. 대 부분의 Vendor Tool에는 Gate Counter가 내장되어 있다. (없는 것도 있지만)

가장 최적화 되어있는 방식을 채택하는 것이 좋겠다. 이것은 가르쳐 줄 수 있는 문제가 아니라 자기 자신이 직접 경험으로 아는 것이 중요하다.

문법(?)적인 설명을 하자면 예제3의 When-else 문은 Process 문에서는 사용될 수 있는 코 딩이다. 마찬가지로 Case-when 문은 Process문 밖에서는 사용될 수 없다. 지금 현재는 모 든 코딩을 Signal Assign으로 가고 있다. Signal 뿐만 아니라 Variable 이라는 것도 있다는 것을 알고 있기를 바란다. (Variable Assign은 ':= '이다.) Signal 과 Variable을 지금 동시 에 설명한다면 현재로서는 이해하기 어려울 것이다. 그래서 그 부분은 잠시 미루기로 하겠 다.

Case-when은 범용 적으로 잘 사용되는 스타일이므로 잘 기억하기 바랍니다.!! std\_logic은 1비트를 설명하는 것이며 1비트 이상에서는 std\_logic\_vector(n downto 0) 사용합니다. std\_logic\_vector(n downto 0)는 n비트를 표시하는 것이며, 여기서 n은 MSB 를 나타내는 것입니다. 또한 std\_logic\_vector(0 to n)는 0이 LSB를 표시합니다. 또, 1비트에서는 '0' 또는 '1'을 표시하고 1비트 이상에서는 "00" 큰따옴표를 사용해요.

그럼 2-way 4×1 Multiplexor를 한 번 설계해 보세요. 그러니까 입력 4개가 각각 2비 트이고, 출력이 2비트를 설계하는 것입니다. 그리고 4-way 4×1 Multiplexor를 한 번 스스로 설계해 보세요. (숙제)

그리고 참조로 말씀드리면 대부분의 고급 설계 Tool은 Unix 환경에서 작동하는 것이 많습니다. 그러니 당연히 Unix의 기본은 알고 있어야 하겠죠. Unix 환경을 구하기 힘들 다면 Linux를 한 번 시도해 보는 것도 좋습니다. vi 에디터 정도는 기본적으로 알고 있 어야 합니다.

# 조금 복잡한 MUX

그럼 2-way 4×1 Multiplexor를 한 번 설계해 보세요. 그러니까 입력 4개가 각각 2비 트이고, 출력이 2비트를 설계하는 것입니다. 그리고 4-way 4×1 Multiplexor를 한 번 스스로 설계해 보세요. 이것이 숙제였죠.

-- 2-way 4×1 Multiplexor -- 4-way 4×1 Multiplexor library ieee; library ieee; use ieee. std\_logic\_1164.all; use ieee. std\_logic\_1164.all; entity mux41 is entity mux41 is **port** (a, b, c, d : in std\_logic\_vector(1 **port** (a, b, c d : in std\_logic\_vector(3) downto 0); downto 0); sel : in std\_logic\_vector(1 downto 0); sel : in std\_logic\_vector(1 downto 0); y : **out** std\_logic\_vector(1 downto 0)); y : **out** std\_logic\_vector(3 downto 0)); end mux41; end mux41; architecture rtl of mux41 is architecture rtl of mux41 is begin begin process(sel) process(sel) begin begin case sel is case sel is **when** "00" => y <= a; **when** "00" => y <= a; **when** "01" => y <= b; **when** "01" => y <= b; when "10" =>  $v \le c$ ; when "10" =>  $v \le c$ ; when others => y <= d;when others => y <= d;end case; end case; end process; end process; end rtl; end rtl;

앞에서 std\_logic은 nine values를 가지고 있다고 했습니다. 기억이 납니까? 그것을 이용하죠. 입력이 4비트의 6개의 입력을 가진 MUX를 한번 설계해 봅시다. 입력이 6개이면 이것을 선택하는 Select 단자는 3개가되어야 하겠죠. 그럼 입력이 6개임으로 2개의 단자는 don't care로 처리하는 것이 당연하겠죠. 꼭 don't care로 처리할 필요는 없습니다. 그렇지만 임의로 don't care로 처리합시다.

```

ex1)

library ieee;

use ieee. std_logic_1164.all;

entity mux41 is

port (a, b, c, d, e, f : in std_logic_vector(3 downto 0);

sel

: in std_logic_vector(2 downto 0);

: out std_logic_vector(3 downto 0));

У

end mux41;

architecture rtl of mux41 is

begin

process(sel, a, b, c, d, e, f)

begin

case sel is

when "000" => y <= a;

when "001" => y <= b;

when "010" => y <= c;

when "011" => y <= d;

when "100" => y <= e;

when "101" => y \leq f;

when others => y <= "----";

end case;

end process;

end rtl;

그렇게 문법적인 내용은 없지요. Architecture Body의 마지막 문장에 주의해서 보십시오.

when others => y <= "----";

v의 출력 값으로 보내는 것이 "----"이지요. 이것이 don't care로 처리하는 것입니다.

std_logic의 nine values 중의 하나인 don't care입니다.

'U', -- Uninitialized

'X', -- Forcing Unknown

'1', -- Forcing 1

'0', -- Forcing 0

'W', -- Weak

Unknown

'Z', -- High Impedance

```

```

'L', -- Weak 0 'H', -- Weak 1

```

```

'-' -- Don't care

```

이 nine values는 Standard Library에 정의되어 있습니다. 보통 라이브러리 디렉토리를 열어 보면 std1164.vhd라는 파일이 있습니다. 이 속에 정의되어 있습니다.

library ieee; use ieee. std\_logic\_1164.all; 이 구문이 Standard Library를 사용하겠다는 말입니다. 앞에서 이 파일을 구경해 보라고 말 씀드린 것 같은데 구경은 해 보았습니까? 해보지 않았다면 이 강좌에서는 네 가지의 다른 툴의 Library 파일을 동봉하겠습니다. 편의상 파일명을 바꾸어서 올려 드리겠습니다.

Altera. vhd - Max Plus 피의 std1164.vhd 파일 synopsis. vhd - Synopsis의 std\_logic\_1164.vhd 파일 lodecap. vhd - ETRI의 std\_logic\_1164.vhd 파일 xilinx - Xilinx의 stdlogic.vhd 파일

그냥 메모장으로 링크 하면 읽을 수 있습니다. 한 번 보세요. 회사마다 조금의 차이는 있지 만 표준 규격은 같다는 정도만 아시면 됩니다. 얼마나 툴을 최적화 하느냐 하는 차이겠죠.

다시 본문으로 가서 초기화되지 않은 상태로 두고자 한다면 when others => y <= "uuuu";로 처리하면 되겠지요. 여기서 대문자 소문자는 별 의미가 없습니다. 그러나 Unix에서는 주의하셔야 합니다. 파일명 등에서 대소 문자를 혼동하면 안 되겠지요. Reserved word에서는 별 의미가 없습니다. 또는 when others => y <= "0000";로 영으로 정하면 되겠지요.

지금 하고 있는 디지털 논리 회로는 문법적인 면에서는 별로 어렵지 않습니다. 그러나 그 기능은 반드시 알고 있어야 합니다. 예를 들어 Mux는 입력이 들어오면 그 중에 하나를 선 택하는 것이라는 기능은 반드시 알아야 합니다. 이런 간단한 회로들은 Logic으로 구현되어 Symbol로 정의가 되어 있습니다. 완성된 것을 설계하는 것은 별로 의미가 없지만 VHDL의 설계에서는 가장 기초가 되는 내용이니 하찮게 여기지 맙시다.

RTL Level, synthesis이니 하는 어려운 내용은 기초적인 것이 끝나면 정리하기로 하겠습니 다. 여러 가지를 설계하다 보면 그 과정이 어떻게 수행되는지 더 잘 이해가 되기 때문에 나 중으로 미루고 있습니다. 제 방식이 마음에 들지 않겠지만 제 경험으로는 이 방법이 더 좋 을 것이라 생각됩니다. 그리고 이 글을 보시는 분은 적어도 VHDL이 무엇인지 한번은 들어 본 사람이라고 생각됩니다. IDEC에서 강의를 들을 때 이론만으로 이해하기는 힘들었습니다. 그리고 모든 장의는 원론에서 시작합니다. VHDL의 가장 핵심이 되는 내용을 이론만으로 다 이해하기는 힘들었습니다. 그래서 저는 기초 과정을 두 번 들었습니다. 그러니 어느 정도 이해가 되었습니다. 원래 엿장수 마음대로 이니까요 !!!

다음 예제는 Enable을 갖는 4-way 4×1 multiplexor입니다. 여기에는 가장 빈도가 높은 If-else 구문이 사용됩니다. 잘 봅시다.

```

ex2)

library ieee;

use ieee. std_logic_1164.all;

entity mux41 is

port (a, b, c d : in std_logic_vector(3 downto 0);

enable : in std_logic;

sel : in std_logic_vector(1 downto 0);

: out std_logic_vector(3 downto 0));

У

end mux41;

architecture rtl of mux41 is

begin

process(sel)

begin

if (enable='0') then

case sel is

when "000" => y <= a;

when "001" => y <= b;

when "010" => y <= c;

when others => y <= d;

end case;

else

y <= "0000";

end if;

end process;

end rtl;

if-else 구문은 다음과 같은 형태를 합니다.

if (조건) then

수행식;

else

수행식;

end if;

```

if-else 구문은 순차적으로 진행되므로 **반드시 Process 문안에서 실행됩니다.** 중요한 사항 입니다. 언어의 형태와 비슷하죠. 괄호는 필요한 사항은 아닙니다만 자기가 보기가 편하기 때문에 저로 주로 괄호를 이용합니다. Enable 신호가 있으면 0000으로 Set되고 Enable 신호가 영이면 Mux의 기능을 수행합니다. 라이브러리에서는 Symbol로 구현되어 있으므로 반드시 그 형태를 따라가야 하지만 VHDL 에서는 자기 자신에 맞는 코딩을 할 수 있다는 것은 굉장히 유용한 사실입니다.

```

다음은 Decoder와 Encoder에 대해서 알아보기로 하겠습니다. 기능은 모르고 있다면 디지털

논리 회로를 참조하기여 알아보시기를 바랍니다.

ex3) 2-to-4 decoder

library ieee;

use ieee. std_logic_1164.all;

entity decoder is

port ( a : in std_logic_vector(1 downto 0);

d : out std_logic_vector(3 downto 0));

end decoder;

architecture decoder1 of decoder is

begin

process

begin

case a is

when "00" => d <= "0001";

when "01" => d <= "0010";

when "10" => d <= "0100";

when others => d <= "1000";

end case;

end process;

end decoder1;

decoder라는 개념은 나중에 살펴볼 One-hot Coding이라는 개념과 비슷할 것입니다. 칩의

크기는 커지지만 Performance는 증가한 다는 것을 알 수 있을 것입니다.

```

```

architecture name이나 entity name이 reserved word와 이름이 달라야 한다고 말씀 드렸지

요. 그럼 reserved word는 어떤 것이 있는지 살펴봅시다.

```

abs access after alias all and architecture array assert attribute begin block body buffer bus case component configuration constant disconnect downto else elsif end entity exit file for function generate generic guarded if in inout is label library linkage loop map mod nand new next nor not null of on open or others out package port procedure process range record register RAM report return select severity signal subtype then to transport type units until use variable wait when while with xor

조금 생소한 느낌을 주는 것들이 많지요. entity name이나 architecture name이 위의 이름 을 가지면 안 된다는 뜻이죠. and는 안 되지만 andl은 다른 의미를 가지므로 가능하겠죠. 위의 내용은 그렇게 어려운 내용이 아니므로 그냥 넘어갑니다. Encoder에 대해서 알아봅시 다.

```

ex4) 4-to-2 decoder

library ieee;

use ieee. std_logic_1164.all;

entity encoder is

port ( a : in std_logic_vector(3 downto 0));

z : out std_logic_vector(1 downto 0));

end encoder;

architecture encoder1 of encoder is

begin

z <= "00" when a(0) = '1'

else "01" when a(1) = '1'

else "10" when a(2) = '1'

else "11";

```

end encoder1;

여기서 a(0)라고 하는 것은 입력 a가 4비트이므로, 4비트의 LSB(최하위 비트)를 말하는 것 입니다. a(3)이라고 한다면 MSB(최상위 비트)를 말하는 것입니다. 이 구문은 앞에서 다른 적이 있는데 기억하고 있습니까? Concurrent 문에서 사용되는 구문이라고 앞에서 설명 드 렸지요. 논리 회로의 기초적인 지식이 없으면 아무리 제가 쉽게 설명한다고 해도 따라오기 가 힘들 것입니다. 부족하다고 느끼시면 다시 시작하십시오. 지금은 늦은 때가 아닙니다. 앞 으로도 너무 많은 것이 남아 있습니다. 제가 언제 이것을 다할 지는 모르겠지만 하는데 까 지는 해 봅시다. 자신감을 가지세요.

## Increment, Decrement, 비교 연산 회로

오늘은 Increment, Decrement, 비교 연산 회로에 대해서 알아보기로 하겠습니다. Increment는 입력을 받으면 +1을 해서 출력으로 내보는 것입니다. 원래 ALU의 기능에 포 함되지만 독립적으로 해석해 보겠습니다. 클럭을 입력받아야 하지만 클럭의 기능은 빼고 시 작하겠습니다. Decrement는 그 반대로 -1의 기능을 수행합니다. 예를 들자면 입력이 3이라 고 가정하면 Increment는 4를 출력할 것이고, Decrement는 2를 출력할 것입니다. 비교기는 간단히 말해 그 입력을 비교하는 것입니다. 여기서는 a가 b보다 크면 1을 출력할 것이고 b 가 크면 0을 출력할 것입니다. 간단한 논리 회로입니다. 간단하다고 생각되지만 이 기능이 나중에 큰 기능을 담당합니다.

ex1)

library ieee; use ieee. std\_logic\_1164.all; use ieee. std\_logic\_signed. all;

entity inc is

port ( pc\_in : in std\_logic\_vector(4 downto 0);

pc\_out : out std\_logic\_vector(4 downto 0));

end inc;

architecture rtl of inc is begin pc\_out <= pc\_in + 1;</pre>

end rtl;

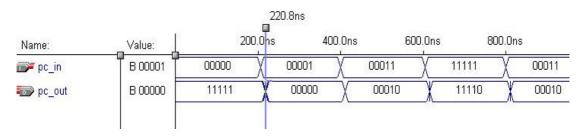

여기에서는 결과 파형을 조금 살펴봅시다.

| pc_in B 00001 00000 ¥ 00001 ↓ 00011 ↓ |         |       |

|---------------------------------------|---------|-------|

|                                       | 11111 χ | 00011 |

| n pc_out B 00001 00001 00010 00100    | 00000   | 00100 |

입력이 0, 1, 3, 1f, 3으로 되어 있습니다. 파형을 관찰할 때 주의 할 점은 모든 구간의 영역 을 다 살펴보아야 합니다. 5비트 입력이므로 0h에서 1fh까지 모두 살펴보아야 하지만 사실 그러기는 어렵죠. 그래도 시작점과 끝 부분 그리고 입력이 바뀔 수 있는 부분은 모두 체크 해야 합니다. 그리고 이 그림에서 알 수 있는데 delay라는 것을 느낄 수가 있죠. 그리고 왜 입력이 4비트가 이니라 5비트인가? 이 점에 대해서 살펴보아야 할 것입니다. Intel의 기본은 8비트입니다. 그러나 이 8비트는 4비트 두 개가 모여서 8비트를 이루는 것입니다. 4비트 연 산을 위해서는 5비트의 공간이 필요합니다. 여기에서 보면 11111이 입력입니다. 출력은 00000으로 나와 있지만 값은 원래 값은 100000이 될 것입니다. 그러면 왜 출력을 6비트로 정의하지 않았느냐 하는 질문을 할 수 있을 것입니다. 그러나 상태 Flag에서 이 값을 체크 해 carry로 그 값을 보낼 것입니다. 지금은 간단하게 5비트 입력, 5비트 출력 이렇게 되어 있지만, 다음에 살펴볼 ALU에서 입력이 4비트 출력이 4비트인 회로를 설계할 것입니다. 그 때는 내부 Signal이라는 것을 이용하게 될 것입니다. 내부 시그널은 다음, 다음 시간에 배우 게 될 것입니다.

우리가 지금까지 사용하지 않은 구문이 있군요.

**use** ieee. std\_logic\_signed. all;

사용하는 Values가 signed 값을 사용한다는 의미입니다. 여기서는 그렇게 큰 의미는 없지만 unsigned 값을 사용한다면 달라지겠죠.

다음은 Decrement 회로를 정의해 볼까요. ex2) library ieee; use ieee. std\_logic\_1164.all; use ieee. std\_logic\_signed. all;

entity dec is

# architecture rtl of dec is begin

pc\_out <= pc\_in - 1; end rtl;

+, - 기호 하나만 바꾸면 됩니다. 그리고 결과는 다음과 같습니다.

만약 signed package가 없다면 어떻겠습니까?

-- use ieee. std\_logic\_signed. all;

```

주석으로 처리한 후 컴파일을 해보세요. 결과가 어떻게 나오는지?

ex3) less than 비교 연산 회로

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_signed. all;

entity less is

port ( a, b : in std_logic_vector(1 downto 0);

z : out std_logic);

end less;

architecture rtl of less is

begin

process(a, b)

begin

if (a < b) then

z <= '1';

else

z <= '0';

end if;

end process;

end rtl;

간단한 비교기를 보았는데 less than만 될까요? 아닐 것 같지요. 그럼 변형을 해봅시다.

if (a < b) then -- b가 a보다 크다면

if (a > b) then -- a가 b보다 크다면

if (a <= b) then -- b가 a보다 크거나 같다면

if (a >= b) then -- a가 b보다 크거나 같다면

if (a = b) then -- a와 b가 같다면

if (a /= b) then -- a와 b가 같지 않다면

한 줄을 바꿈으로서 6개의 회로를 설계할 수 있습니다.

관계 연산자는 위의 6가지 형태입니다. 유용하게 쓰일 때가 있을 것입니다.

오늘은 간단하게 끝내겠습니다. 제가 좀 피곤해서요.

```

다음 시간에는 D Flip-flop에 대해서 설계하도록 하겠습니다. FF과 Latch의 차이점을 미리 알아두시는 것이 편할 것입니다.

# DFF과 latch

우리는 제일 먼저 논리 회로에서 AND, OR, NOT 게이트를 먼저 배우고 그 다음에 NAND, NOR 게이트를 배우게 됩니다. AND, OR의 기능을 가지면 NAND와 NOR를 설명 하기 쉽기 때문입니다.

그러나 실제 회로에서는 그 개념이 아닙니다. 회로의 최적화를 이루기 위해서는 AND나 OR 보다는 NAND와 NOR 게이트를 가지고 설계하는 것이 가장 최적화 되어 있는 회로입니다. 집적회로의 입장에서 보면, PNP Junction에서 NMOS와 PMOS를 가지고 설계할 수 있는 가장 기본의 형태가 Nand, Nor 게이트입니다.(집적회로까지 설명하면 너무 깊이 들어가야 함으로 간단하게 설명하겠습니다. 궁금한 점이 있는 집적회로를 공부하는 것이 도움이 될 것입니다. Spice Tool을 이용하여 간단한 Layout 설계를 해보시면 알 것입니다.) NAND 게 이트는 and 게이트에 not 게이트를 붙여서 설계한 회로입니다. 그러니 NAND, NOR, NOT 가 회로의 기본입니다. NAND만 보면 PMOS 두 개를 병렬로 연결하고 NMOS 두 개를 직 렬로 연결한 것이 NAND 회로입니다. 참고로 말씀드리면 설계의 기본은 Layout 과정입니 다. 배워 두시면 도움이 될 것이라 생각은 들지만 시간이 많이 걸린다는 것이 단점입니 다.(?) 그럼 ASIC 설계에서 가장 기본적으로 알아야 하는 것은 무엇일까요? 아마도 DFF 이라고 저는 생각하는 데요. 이제 설계자의 입장에서 말씀드리겠습니다. 기본적인 회로의 설 계가 끝나면 여러분은 설계자 입장에서 모든 것을 생각하고 설계를 해야 합니다. 하드웨어 디자이너가 되는 것입니다. 기쁘겠죠.

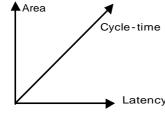

디자이너가 가장 중요하게 생각해야 하는 Factor가 네 가지 있습니다. 아니 더 많을 수도 있지만 기본적인 4가지가 있습니다. 그 중에 한 가지인 Area(yield and packaging cost) 문제가 있습니다. 그 문제가 인해 **회로 면적이 적게 차지하는 DFF을 이용하는 것**입니다. 그래서 VHDL 코딩을 하면 컴파일을 하고 synthesis를 하고 나서 logic으로 구현된 설계도 를 보면 메모리 소자를 DFF으로 설계된 것을 확인할 수 있을 것입니다. 지금 살펴 볼 문제 는 아니지만 설계시 고려해야 할 4가지 요소에 대해서 설명 드리면 다음과 같습니다.

Serformance :

- Delay and cycle-time.

- Latency.

- Throughput ( for pipeline application).

- Area ( yield and packaging cost).

- Testability

- Power

기분 나쁘게 전부 영어로 작았죠. 다른 사람과 설계에 대해서 이야기를 한다면 영어로 말을 하여 야죠. 다른 사람이 성능이 어때? 라고 묻지는 않을 것입니다. "Performance가 어때? "라고 묻지. 위의 설명은 여러분이 디자이너가 되면 시작할 것입니다. 그 때를 기대하세요. 그렇게 어려운 용어가 아닌지 대강은 감을 잡을 수 있을 것입니다.

지난 시간에 DFF과 latch에 차이에 대해서 알아보셨나요. 부지런한 디자이너는 조사해서 알 아있을 것이고, 귀찮은 사람은 그냥 기다리겠죠. 그러나 이런 단순한 이론에서 오는 차이가 크다는 것을 알아야 합니다. 그만큼 회로 설계시간의 단축을 가져올 수 있습니다.

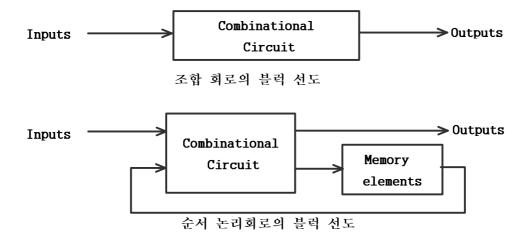

이 시간을 이해하기 위해서는 조합 회로가 무엇이고 순서 회로가 무엇인지 알아야 합니다.

조합 회로는 임의의 시간에서 출력이 이전의 입력에는 관계없이 현재의 입력 조합으로 부터 직접 결정되는 논리회로를 말합니다. 반면 순서 회로는 출력은 외부로부터의 입력 이 기억 상태를 바꾸게 된다. 즉 순서 회로의 입력, 출력 그리고 내부 상태의 시간에 따 른 순서로서 규정된다. 쉽게 말하면 조합 논리의 결과가 출력이 되는 것이 아니라 메모리 요소에 저장되어 있는 변화된 값이 다시 조합 회로로 궤환되어 결과 값이 출력되는 것이다. 이것은 다시 두 가지로 나누어진다. 클럭 펄스가 들어오는 시점에서 입력 신호로부터 그 동 작을 정의할 수 있는 시스템이 동기형(synchronous) 순서 논리회로이다. 비동기형 (Asynchronous) 순서 회로 동작은 입력 신호가 변화하는 순서에 따라 언제라도 영향을 받 을 수 있다.

Flip-flop이나 latch는 one-bit 메모리 소자입니다. 클럭이 있는 순서 논리회로에 쓰이는 기 억 소자를 플립플롭이라고 한다. FF은 edge-triggered memory device라고 합니다. 이 말 은 플립플롭의 상태는 입력 신호의 순간적인 변화에 따라 바뀌기 때문입니다. 순간적인 입 력 변화를 트리거(trigger)라고 합니다. FF을 흔히 레지스터라고도 합니다.

비동기식 순서 회로에서는 클럭 펄스를 사용하지 않는다. 비동기식 순서 회로에서의 기억 소자로는 클럭이 없는 플립플롭(latch)이거나 시간 지연 소자(time-delay element)를 사용한 다. 비동기식 순서 회로 설계는 타이밍 문제 때문에 설계가 더 어렵습니다.

latch는 level-sensitive memory device입니다. 그 말은 클럭을 사용하지 않기 때문에, 입력 이 변화되는 즉시 시스템의 상태가 변화할 수 있게 되어야 한다는 뜻이죠.

클럭이 있는 동기식 시스템의 예를 많이 보았을 것이고, 비동기식 회로에서는 빠른 동작

속도가 요구될 때 사용합니다. 예를 들자면 그 자체에 독립적인 클럭을 가진 각각의 장치가 있는 2개의 시스템간의 교신은 비동기식 회로로 이루어져야 합니다.

적절한 시스템 설계를 위해서는 동기식의 일부가 비동기식 특성을 갖는 혼합된 시스템을 설계해야 합니다.

그럼 간단히 정리하죠. 동기식 순서 회로에서 사용되는 기억 소자는 플립플롭이고, 비동 기식 순서 회로 사용되는 기억 소자는 레치 입니다. 플립플롭은 클럭이 있고, 레치는 클 럭이 없습니다. 좀 어렵게 설명하면 펄스 지속 시간에 민감한 플립플롭 군을 레치라고 하고, 펄스에 전이에 민감한 플립플롭 군을 레지스터라고 합니다.

이 부분은 조금 중요한 부분이라 조금 길게 설명이 됐는데 되도록 논리회로의 설명은 자제 하는 방향으로 하겠습니다.

오늘은 예제가 조금 많습니다. 플립플롭과 레치에 관계된 예제입니다. 이 부분은 Actel 매뉴 얼에서 인용했습니다. 인터넷 Actel 홈페이지에 가서 다운 받을 수도 있고, 사용자 등록을 하시고 매뉴얼 신청을 하시면 구할 수 있을 것입니다. http://www.actel.com

오늘 예제는 모두 DFF으로 구현된 예제입니다. 다른 플립플롭으로 구현은 아마 힘들 겁니 다. 칩 설계를 위해서 그런 것이니 JKFF, RSFF, TFF 등을 구현하고자 한다면 Logic에서 설계된 것을 이용하시면 될 것입니다.

| ex1) Rising Edge Flip-Flop<br>library ieee;<br>use ieee. std_logic_1164.all; | ex2) D-Latch with Data and Enable<br>library ieee;<br>use ieee. std_logic_1164.all; |  |  |  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| entity DFF is<br>port ( data, clk : in std_logic;<br>q : out std_logic);     | entity d_latch is<br>port ( data, enable : in std_logic;<br>y : out std_logic);     |  |  |  |

| end DFF;                                                                     | end d_latch;                                                                        |  |  |  |

| architecture behav of DFF is                                                 | architecture behav of d_latch is                                                    |  |  |  |

| begin                                                                        | begin                                                                               |  |  |  |

| process(clk)                                                                 | process(enable, data)                                                               |  |  |  |

| begin                                                                        | begin                                                                               |  |  |  |

| if (clk='1' and clk' event) then                                             | if (enable='1') then                                                                |  |  |  |

| $q \leq ata;$                                                                | y <= data;                                                                          |  |  |  |

| end if;                                                                      | end if;                                                                             |  |  |  |

| end process;                                                                 | end process;                                                                        |  |  |  |

| end behav;                                                                   | end behav;                                                                          |  |  |  |

| 에키고리 그런스 키리티크 프장네                                                            | 레이어나 파키네 이구스                                                                        |  |  |  |

생각보다 구현은 간단하죠. process 문안에 재미있는 표현이 있군요.

## if (clk='1' and clk' event) then

#### $q \leq data;$

이 구문은 어떤 의미일까요? 플립플롭에서는 Trigger 방법을 이용한다고 했는데 말이죠. event를 이용해서 상승에지를 표현한 것입니다. 외우세요.

그럼 그 반대로 하강에지를 표현하면 어떻게 될까요? 1을 0으로 바꾸면 되겠죠.

#### if (clk='0' and clk' event) then

q <= data;

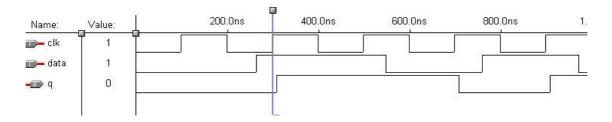

설명할 것은 이것뿐이네요. 다음 예제로 넘어가지 전에 결과를 비교해 볼까요.

그림에서 보듯이 클럭의 입력에 따라 출력이 변한다는 것을 알 수 있습니다.

| Name:Valu | ie: | 200.0ns | 400.0ns | 600.0ns | 800.0ns | 1.0 |

|-----------|-----|---------|---------|---------|---------|-----|

| ᢇ enable  | 1   |         |         |         |         |     |

| 🗩 data    | 1   |         |         |         |         |     |

| -💿 у      | 1   | 8       |         |         |         |     |

레치는 입력에 따라 값이 변한다는 것을 알 수 있을 것입니다.

그림이 조금 정확하게 보이지 않는데 주의해서 보시면 될 것입니다.

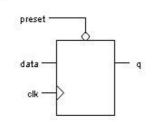

ex3) Rising Edge Flip-Flop with Asynchronous Reset library ieee; use ieee. std\_logic\_1164.all;

architecture behav of DFF is

begin

process(clk, reset)

begin

```

if (reset='0') then

a <= '0';

elsif (clk='1' and clk' event) then

data

q \leq data;

clk

end if;

end process;

reset

end behav;

설명할 것이 없네요. 말 그대로입니다. reset을 가진 플립플롭입니다. 다만 reset이 0일 때

플립플롭의 기능을 수행하겠죠. 코딩은 reset이 1일 때라고 의문을 가지는 분은 위의 그림을

유심히 보시면 됩니다. reset에 not가 붙어 있죠.

ex4) Rising Edge Flip-Flop with Asynchronous Preset

library ieee;

use ieee. std_logic_1164.all;

entity DFF is

port ( data, clk, preset : in std_logic;

: out std_logic);

q

end DFF;

architecture behav of DFF is

begin

£,

```

```

begin

if (preset='0') then

q <= '0';

elsif (clk='1' and clk' event) then

q \leq data;

end if;

end process;

end behav;

```

process(clk, preset)

q

C 언어에서 if-else 구문이 있죠. 이것과 사용법은 거의 비슷합니다. 다만 C 언어에서는 else if 라고 쓰지만, VHDL에서는 elsif 라고 씁니다. 다른 언어와 틀리니 주의하세요. 다른 언어에서처럼 if 구문 속에 if 문이 계속해서 들어갈 수 있습니다. 나중에 예제에서 보 겠죠.

```

ex5) Rising Edge Flip-Flop with Asynchronous Reset and Preset

library ieee;

use ieee. std_logic_1164.all;

entity DFF is

port ( data, clk, reset, preset : in std_logic;

: out std_logic);

q

end DFF;

architecture behav of DFF is

begin

process(clk, reset, preset)

begin

if (reset='0') then

q <= '0';

elsif (preset='0') then

q <= '0';

elsif (clk='1' and clk' event) then

q \leq data;

end if;

end process;

end behav;

```

```

Asynchronous Reset and Preset은 시스템이 불안정할 수 도 있다는 것을 알고 있어야

합니다. Asynchronous Reset and Preset보다는 Synchronous Reset and Preset이 안

정적이라는 것을 알고 있어야 합니다. 다시 말하면 Asynchronous Reset은 클럭에 관

계없이 Reset이 1이면 모든 것을 리셋 시키는 기능을 합니다. 그렇지만 시스템 회로 설

계에는 Asynchronous Reset이 더 많이 사용되고 있습니다.

```

ex6) Rising Edge Flip-Flop with Synchronous Reset

library ieee;

use ieee. std\_logic\_1164.all;

```

architecture behav of DFF is

begin

process(clk)

begin

reset

if (clk='1' and clk' event) then

gnd

if (reset='0') then

q

data

q <= '0';

else

clk

q \leq data;

end if;

end if;

end process;

end behav;

위 그림을 보면 어떤 의미인지 알 수 있을 것입니다.

Synchronous Reset을 사용하므로 훨씬 안정적인 회로이겠죠.

ex7) Rising Edge Flip-Flop with Synchronous Preset

library ieee;

use ieee. std_logic_1164.all;

entity DFF is

port ( data, clk, preset : in std_logic;

: out std_logic);

q

end DFF;

architecture behav of DFF is

begin

process(clk)

begin

if (clk='1' and clk' event) then

if (preset='0') then

q <= '0';

else

q \leq data;

end if;

end if;

end process;

end behav;

```

ex8) Rising Edge Flip-Flop with Asynchronous Reset and Clock Enable library ieee; use ieee. std\_logic\_1164.all; entity DFF is **port** ( data, clk, reset, en : in std\_logic; : **out** std\_logic); q end DFF; architecture behav of DFF is begin process(clk, reset) begin if (reset='0') then q <= '0'; elsif (clk='1' and clk' event) then if (en ='1') then q <= data; end if; end if; end process; end behav;

Asynchronous Reset과 Clock이 Enable 될 때 data에 있던 값이 q로 assign 되는 것입니 다. 한 가지 예제를 알면 응용하는 범위가 VHDL은 굉장히 넓기 때문에 많은 회로를 쉽게 만들 수 있다는 이점이 있습니다. 우리가 설계한 회로를 라이브러리에 저장해 그것을 불러 서 사용할 수도 있습니다. REUSE 가능한 언어가 VHDL입니다.

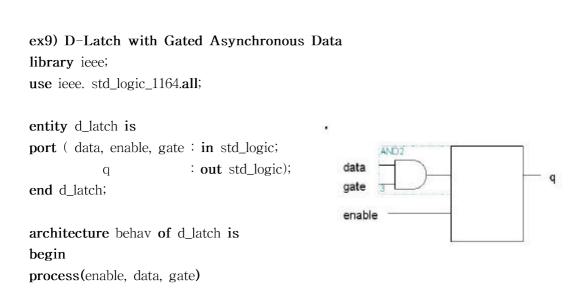

begin

if (enable='1') then

q <= data and gate;

end if;

end process;

end behav;</pre>

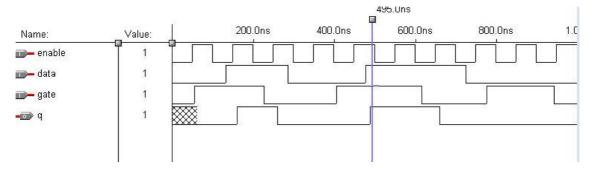

레치의 간단한 변형입니다. 그렇게 어려운 것은 없고 출력 값이 변하는 것을 유심히 살펴 보기를 바랍니다. 클럭이 시작될 때 변하는 것이 아니라 enable이 1인 영역에서 data와 gate 가 둘 다 1인 시점에서 변한다는 점을 시뮬레이션 결과에서 잘 살펴보기를 바랍니다.

ex10) D-Latch with Gated Enable library ieee; use ieee. std\_logic\_1164.all;

architecture behav of d\_latch is

begin

process(enable, data, gate)

begin

if ((enable and gate)='1') then

q <= data;

end if;

end process;

end behav;</pre>

if 구문 안에 어떤 것이 변하는지 잘 보면 될 것입니다. 그냥 넘어갑니다.

```

ex11) D-Latch with Asynchronous Reset

library ieee;

use ieee. std_logic_1164.all;

entity d_latch is

port ( data, enable, data : in std_logic;

: out std_logic);

q

end d_latch;

architecture behav of d_latch is

begin

process(enable, data, reset)

begin

if (reset='0') then

q <= '0';

elsif (enable='1') then

q \leq data;

end if;

end process;

end behav;

```

간단한 예제들을 중심으로 플립플롭과 레치에 대해서 알아보았습니다. 8비트 레지스터를 설 계하다 보면 이 부분에 대해서 다시 한번 살펴볼 기회가 있을 것이라 생각됩니다. 위 예제 들을 직접보고 코딩하지 마시고, 이런 기능을 가지고 있으므로 어떤 식의 설계가 들어가야 한다라고 자꾸 생각하시면서 직접 설계해 보시는 것이 기억에 오래 남을 것입니다. 전에도 말씀드렸지만 자기 자신의 고유의 코딩 방식을 절대로 잊지 마십시오.

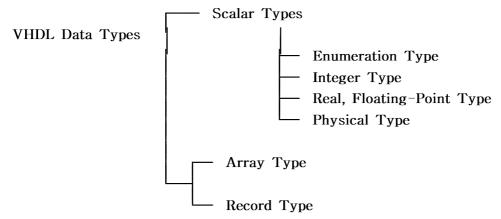

## VHDL의 자료형과 객체형

VHDL의 자료형과 객체형, Signal과 Variable과 Constant에 대해서 배우게 될 것입니 다. 오늘 배울 것은 VHDL의 자료형과 객체형입니다. 이제까지는 std\_logic과 bit\_logic 그 리고 Array인 std\_logic\_vector 만을 배웠습니다. 다른 언어들처럼 VHDL도 많은 자료형을 사용할 수 있습니다.

VHDL에서 자료형 검사는 매우 엄격하며 정의된 자료형에 따라 사용할 수 있는 연산자 또한 각각 정의되어야 합니다. 합성기(synthesizer)에 따라 서로 지원하는 데이터형이 다를 경우 VHDL 소스 사이의 호환성에 심각한 문제를 일으키며 많은 자료형 변환 함수와 타입 캐스팅 방법이 존재하게 된다. 이러한 문제를 해결하기 위하여 87년 IEEE 1076 VHDL의 표준에 이어 1991년에 IEEE 1164로서 디지털 회로의 합성 가능한 자료형에 대한 표준이 제 정되기에 이르렀다. IEEE 1164는 디지털 회로에 대하여 9 가지 값(standard 9-valued logic) 을 갖는 데이터 형 "std\_logic"을 정의하였고, 이는 IEEE 1076 의 "bit" 형을 확장한 것 이다. IEEE 1076에는 VHDL의 언어에 대한 표준과 아울러 데이터 타입 및 각종 연산에 대 한 표준이 정해져 있다. IEEE 1076에는 디지털 회로의 비트(bit) 형과 정수 및 실수형 문자 형 등이 있으며 이중 bit와 정수형이 합성 가능하다.

IEEE 1164의 "std\_logic"은 bit의 '1'과 '0'이외에 Pull-up, Pull-down에 해당하는 'H' (Weak-High), 'L' (Weak-Low)과 'Z' (high-impedance), 'U' (uninitialize),

'X' (unknown), '- '(Don' t care)등을 정의해 놓음으로써 디지털 회로의 합성뿐만 아 니라 시스템 인터페이스에 대한 배려를 해 두었다.

우선 용어부터 정리를 할까요. VHDL에서 signal, variable, constant 등과 같이 어떠한 값 을 가지고 있는 것을 객체(Object)라고 하며, 모든 object는 data type을 갖는다. 각 object가 가지는 data type은 시뮬레이션 도중에는 변하지 않는 정적(static)이다.

<u>signal</u> <u>a, b</u> : <u>std logic</u>; 객체 선언 객체 자료형(data type)

우선 VHDL에서 사용하는 3가지 객체 종류에 대해선 먼저 살펴봅시다.

- 1. Signal(신호)

- ex) signal a, b, c : bit; c <= a and b;

#### 2. Variable(변수)

ex) variable temp : bit; temp := a and b;

#### 3. Constant(상수)

ex) constant p1 : integer := 314; 위의 세 가지 객체형은 다음 시간에 자세하게 다루게 됩니다. 그럼 다음은 어떤 데이터 타입이 있는지 어디 한번 봅시다.

#### 1. 열거형 (Enumeration type )

기본적으로 VHDL에서 사용하는 대부분의 자료형은 대부분 열거형 (enumeration type) 이 다. IEEE 1076의 standard package에 정의되어 있는 열거형의 예를 들면 다음과 같다.

type boolean is (false, true); type bit is ('0', '1');

IEEE 1164에 std\_logic은 다음과 같이 열거형으로 정의되어 있다. TYPE std\_logic IS ( 'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-' );

'U'는 초기화되지 않은 상태(Uninitialized)를 의미하며 'X'는 Unknown으로서 디지털 값 의 충돌 등과 같은 에러 상태를 나타낸다. '0' 과 '1'은 디지털 값에 해당하며 'Z'는 High Impedance, 'W', 'L', 'H'는 각각 Weak Unknown, Weak 0, Weak 1로서 Pull-up혹은 Pull-down된 디지털 값을 나타낸다. 끝으로 '- '은 합성 시 논리 최적화에 Don't care로 서 이용된다. 열거형을 이용하면 사용자는 언제든지 자료형의 정의가 가능하다. 또한 열거형 으로 정의된 경우 인코딩(encoding) 방법을 지정할 수 있다. 인코딩 방법으로는 2진 코드에 의한 방법(binary)과 One-Hot Encoding이 있다. One-Hot encoding 방법은 유한 상태 머신 (FSM : Finite State Machine)에서 상태를 나타내는 경우에 많이 이용되는 방법이다. 다음 과 같은 예를 살펴보자.

type state is (idle, receive, send); 와 같이 정의된 자료형 "state"의 경우 binary와 One-Hot encoding 되었을 때 차이는 다 음과 같습니다.

type state is (idle, receive, send)

|                  | Bit2 | Bit1 | Bit0 |         | Bit1  | Bit( |

|------------------|------|------|------|---------|-------|------|

| Idle             | -    | -    | 1    | Idle    | 0     | 0    |

| Receive          | -    | 1    | _    | Receive | 0     | 1    |

| Send             | 1    | -    | _    | Send    | 1     | 0    |

| One-hot Encoding |      |      |      | Binary  | Encod | ing  |

예제에서와 같이 열거형 "state"는 3개의 요소를 가지므로 Binary encoding하면 2비트

가 필요한 반면 One-Hot encoding하는 경우 각 요소마다 1개의 비트를 할당하여 3비트로 표현된다. 잠시 소개가 있었지만, 회로의 Performance를 고려할 때 One-hot Coding은 아주 유용한 방식 중에 하나이다. VHDL에서 형 검사(type checking)가 치밀한 이유 중 하나가 위와 같은 열거형을 주로 다루기 때문이라고 할 수 있다. 각종 연산자 혹은 할당 (assignment)의 경우 기본적으로 열거형으로 이루어진 서로 다른 두 타입은 비트 폭에서부 터 다르기 때문이다. 다음과 같이 bit 형과 std\_logic형의 할당문의 경우 예를 살펴보자.

Type bit is ( '0' , '1' ); Type std\_logic is ( 'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-' );

와 같이 정의된 두개의 시그널을 사용한 할당문은 하드웨어적인 연결의 의미를 고려해 볼 때 할당문은 성립할 수 없는 것이 당연하다.

```

Signal A : bit;

Signal B : std_logic;

A <= B;

```

#### 2.. 정수형 (Integer Type)

IEEE 1076에 정의된 정수형의 기본적인 비트 폭(bit-width)은 32비트로 되어 있다.

type integer is range -2147483648 to 2147483647;

정수형은 산술 연산이 가능하며 2의 보수 형태로 이루어진다. 또한 정수형은 합성이 가능 하며 범위를 지정하지 않을 경우 32비트가 된다. 따라서 과도한 비트 폭을 갖는 연산기의 합성을 피하려면 정수의 범위를 지정해서 사용하도록 한다. 다음의 예는 4비트 Signal을 선 언한 예이다.

Signal count : integer range 0 to 15; Signal count : std\_logic\_vector(3 downto 0);

```

ex1)

library ieee;

use ieee. std_logic_1164.all;

```

```

entity add is

```

port ( a, b : in integer range 0 to 15;

```

c \vdots out integer range 0 to 15);

```

end add;

architecture rtl of add is

#### begin

c <= a + b;

end rtl;

위의 예제는 4비트 Adder를 설계한 것이다. 다음과 비교해 보라.

ex2) library ieee; use ieee. std\_logic\_1164.all;

architecture rtl of add is begin

c <= a + b;

end rtl;

구현을 해보면 같은 회로라는 것을 알 수 있다. 그러나 수학적인 연산 기능을 수행할 때 비 트 단위로 계산하는 것보다는 Integer로 변환해서 사용하는 것이 이해에 훨씬 도움을 줄 것이다.

## 3. 실수형 (Real, Floating-Point Type)

실수형(real type)은 합성 가능하지 않다. 시스템 모델링이나 아날로그 회로의 모델링 등 에 사용될 수 있다. IEEE 1076의 실수형의 정의는 다음과 같다.

type real is range -1.0E38 to 1.0E38;

실수형의 디폴트 범위가 위의 범위이다. 그렇지만 우리가 설계하는 회로가 위의 범위를 항 상 사용하는 것은 아니다. 그래서 범위를 지정해 주는 것이 효율적일 것이다.

# 4. Physical Type

물리량의 단위(unit)와 배수 관계를 정의한 것이며 합성 가능하지 않다. IEEE 1076에는 시간에 대한 정의가 있는데 다음과 같다.

time is range -2147483647 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

위에서 볼 수 있듯이 VHDL의 최소 시간 단위는 fs (femto second, 10E-15) 이다.

## 5. 배열형 (Array Type)

VHDL에서 배열형을 사용할 수 있다. 일 차원 배열형의 경우 대부분 합성기에서 지원 하 지만 2차원 배열을 지원하지 않는 합성기도 많다. 디지털 회로의 기본 데이터 단위는 "bit "이다. 이를 버스 형태로 정의하기 위해서 "bit\_vector"형을 사용한다. 즉 버스를 정의하 는 것은 "bit"의 일 차원 배열이다. 배열형을 정의 할 때 그 크기를 지정하는 경우가 있고 임의의 배열 크기를 지정할 수도 있다.

type byte is array (7 downto 0) of bit;

일차원 배열로 8-비트 크기의 데이터 타입 "byte"을 정의한 것이다.

TYPE std\_logic\_vector IS ARRAY ( NATURAL RANGE <> ) OF std\_logic;

"std\_logic" 형으로 일 차원 배열형 "std\_logic\_vector"를 선언한 것이다. 이때 배열의 크기 를 제한시키지 않은 것으로서 시그널을 선언할 때 그 크기를 정하여 사용할 수 있다. 배열 형의 선언한 예는 다음과 같다.

Signal byte\_a : byte; Signal count : std\_logic\_vector( 7 downto 0);

#### 6. 레코드 형(Record Type)

VHDL에서는 레코드형을 지원한다. 디지털 회로에서의 레코드형 사용 예는 기계어 명령의 비트맵 표현 등에 이용될 수 있다. 다음은 레코드형의 사용 예이다.

type month\_name is (jan,feb,mar,apr,may,jun,jul,aug,sep,oct,nov,dev);

type date is

record

day : integer range 1 to 31;

month : month\_name;

year : integer range 0 to 4000;

end record;

constant my\_birthday : date := (21, nov, 1963); SIGNAL my\_birthday : date;

my\_birthday. year <= 1963; my\_birthday. month <= nov; my\_birthday. day <= 21; -- 5-bit

-- my\_birthday(0) : LSB

-- my\_birthday(4) : MSB

```

7. 파생형 (Subtype)과 형 변환(Type Conversion)

VHDL에서의 파생형(subtype)을 정의할 수 있으며 다음의 예는 정수로부터 일정한 크기

를 갖는 파생 정수형을 정의한 예이다.

type big_integer is range 0 to 1023;

subtype small_integer is big_integer range 0 to 7;

"small_integer"는 "big_integer"의 파생형으로 정의되었다.

이 경우 파생형 "small_integer"의 의미는 10-비트 크기의 "big_integer"의 하위 4-비

트를 차지하도록 정렬된다는 의미로서 두 데이터형의 호환됨을 나타낸다. 다음의 예는

VHDL에서 자료형 검사(type checking)의 엄격함을 보여준다.

type big_integer is range 0 to 1000;

type small_integer is range 0 to 7;

signal intermediate : small_integer;

signal final : big_integer;

final <= intermediate * 5; -- type mismatch error

위의 예에서 "big_integer"와 "small_integer" 형은 비록 서로 정수형이긴 하지만 서

로 호환 돼지 않는다. 이러한 경우 "small_integer"를 파생형으로 정의함으로서 형 불일치

(type mismatch) 에러를 해결할 수 있다.

type big_integer is range 0 to 1000;

subtype small_integer is big_integer range 0 to 7;

signal intermediate : small_integer;

signal final : big_integer;

final \leq intermediate * 5;

또 다른 방법으로 type casting을 이용할 수 있는데 이 경우는 기본적으로 두 형의 기본형

이 같아야 한다.

type big_integer is range 0 to 1000;

type small_integer is big_integer range 0 to 7;

signal intermediate : small_integer;

signal final : big integer;

final <= big_integer(intermediate * 5);</pre>

```

만일 정수형과 "std\_logic\_vector"형으로 변환하기 위해서는 두 데이터 타이의 기본형이 전혀 다르므로 형 변환 함수(type conversion function)를 사용하여야 한다. 형 변환 함수는 사용자가 임의로 만들어 쓸 수 있으나 IEEE 1164의 산술 패키지(numeric\_std, numeric\_bit) 에는 정수와 "std\_logic\_vector", "bit" 사이의 형 변환을 위한 함수를 다수 가지고 있으 므로 가급적 이를 이용하도록 권장한다. IEEE 1164 라이브러리의 산술 연산과 형 변환 함 수는 합성 가능한 산술 연산을 다루면서 자세히 살펴보기로 한다. 다음의 예는 산술 연산과 형 변환 함수의 이용에 대한 것이다. package my\_type is type big\_integer is range 0 to 1023; subtype small\_integer is big\_integer range 0 to 7; end package; library ieee; use ieee. std\_logic\_1164.all; use ieee. numeric\_std. all; use work. my\_type. all; entity subtype\_test is port ( a : in small\_integer; b : in small\_integer; c : out std\_logic\_vector(9 downto 0) ); end subtype\_test; architecture behave of subtype\_test is signal t\_int : big\_integer; begin t\_int <= a + b; c <= std\_logic\_vector(to\_unsigned(natural(t\_int), 10)); end; 위의 예는 정수 입력을 받아서 연산을 수행한 후 이를 10 비트 크기의 "std\_logic\_vector

위의 예는 정수 입력을 받아서 연산을 수행한 후 이를 10 비트 크기의 "std\_logic\_vector "로 출력하는 경우이다. 입력된 2개의 정수형("small\_integer") a, b를 계산하여 " big\_integer"로 할당한다.

t\_int <= a + b;

사용자 정의형 "big\_integer"인 "t\_int"로부터 std\_logic\_vector"로 변환하는 과정은 약간 복잡하게 보이지만 이러한 변환 과정이 시스템 설계와 서로 다른 모듈 사이의 인터페 이스 할 때 자주 직면하게 되는 문제이므로 잘 이해 해 둘 필요가 있다.

$c \leq std_logic_vector(to_unsigned(natural(t_int), 10));$

Numeric\_std package에 정수-unsigned 변환 함수가 to\_unsigned()로 제공되고 있다. 이 함 수의 argument가 natural이므로 사용자 정의형으로부터 정수형(natural)으로 type-casting 한다. Unsigned 형으로 변환할 것이므로 integer가 아닌 natural로 type-casting 한 것이다. 정수형을 std\_logic\_vector로 직접 변환하는 함수를 가지고 있지 않다. 따라서 to\_unsigned() 함수를 사용하여 정수를 10비트 unsigned로 변환한 후 다시 type-casting 하여 "std\_logic\_vector"인 출력포트에 연결한 것이다. unsigned는 IEEE 1164의 numeric\_std에 다음과 같이 정의되어 있으므로 type-casting이 가능하다.

# type UNSIGNED is array (NATURAL range <>) of STD\_LOGIC; type SIGNED is array (NATURAL range <>) of STD\_LOGIC;

이 변환 과정을 보면 알 수 있듯이 같은 기본형으로부터 파생된 자료형은 type-casting 할 수 있지만 기본형이 다른 경우 형 변환 함수를 써야 한다. 그러나 "t\_int <= a + b;"에서 와 같이 기본형이 같은 파생형(subtype)의 경우에는 변환을 수행할 필요가 없다. 위의 예를 합성한 결과는 그림 4와 같다. 0~7까지의 범위를 갖는 두개의 "small-integer"형 입력이 4 비트로 연산기로 합성된 후 10비트 출력의 하위 4비트로 출력되는 것을 볼 수 있다.

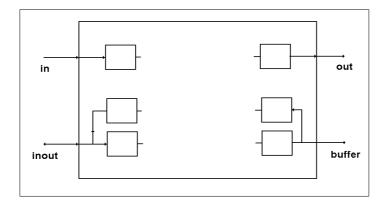

다음은 입출력 타입을 다시 한번 설명하고 넘어가겠습니다. 디지털 신호가 '1' 과 '0' 만 으로 회로를 다룰 것인지 아니면 하이 임피던스(Z)도 있고 풀업(H), 풀다운(L), 그리고 합성 과 시뮬레이션의 상태를 나타내기 위해서 Don't care(-), Unknown(U), 버스 충돌 등에 의 한 에러 상태(X) 등도 구분할 것인지 결정해야 한다. 전자의 경우 bit 타입이라고 하고 후자 의 경우 std\_logic 이라고 하기로 규정했다. VHDL 언어 자체적으로는 std\_logic에 대한 규 정은 없다. 다만 IEEE 1076을 정할 때 std\_logic\_1164 라는 것을 정해 놓고 이곳에 bit라는 것은 1 과 0으로 규정한다거나 std\_logic은 1, 0, Z, H, L, X 등등으로 규정한다고 정했다.

위의 그림이 입출력 포트를 가장 잘 설명한 그림이라고 생각됩니다. IN과 OUT 포트는 잘 이해할 수 있을 것이라 생각됩니다. BUFFER는 INOUT과 같은 입출력 포트로서 assign의 소스(source)측 또는 목적지(destination)측에 쓸 수 있다. INOUT 모드와 다른 점은 단일 할당문 내에서 소스와 목적지측 모두 동시에 사용할 수 있다는 것이다. 이는 BUFFER 모드 에 이미 F/F를 내포하고 있다는 의미를 갖는다. 그림을 자세히 보면 INOUT과 BUFFER의 차이점을 알 수 있을 것입니다.

# Signal과 Variable 그리고 Constant

우선 Constant에 대해서 먼저 설명하겠습니다. Signal과 Variable의 차이점은 좀 미세한 부 분이 많아서 둘을 비교해 가면서 설명하는 것이 좋을 것이라 생각됩니다.

constant는 초기에 선언한 상수의 값을 유지하는데 사용되며 VHDL의 문장 작성에 도움을 주어 쉽게 수정하거나 확장하는데 주로 이용한다. constant의 대입 기호는 ':= '를 사용하고 있다. Variable과 같은 기호를 사용합니다. constant의 초기 값은 즉시 대입되며 한 번 대입 된 값은 바꿀 수 없다. 예를 들자면 Pi 값을 먼저 설정해 두고 계속 사용하면 편리할 것이 다. 사용 방법은 간단하다.

constant p1 : integer := 314; constant length : integer := 345; constant pi : real := 3.1415119;

제가 가장 어렵다고 생각되는 부분이 Signal과 Variable입니다. 이 부분 때문에 너무 많은 고생을 한 기억이 납니다. 차이점을 잘 알고 있어야 합니다.

우선 Signal에 대해서 알아봅시다. signal은 VHDL 합성 시에 Wire(선)로 구성되며, 각 부 품의 연결에 사용되는 외적 변수이다. 세 가지로 사용됩니다.

우선 포트 signal로 사용됩니다. 포트를 정의할 때 사용됩니다.

port ( a, b : in bit; z : out bit); 여기에서 a, b, z는 port signal로 사용되었습니다. 입출력의 정의가 signal로 정의됩니다.

architecture rtl of and\_1 is begin

$z \leq a$  and b; end rtl;

위의 예제에서 보면 알 수 있듯이 포트 시그널로 정의가 되어 있기 때문에 z <= a and b; 라는 표현이 가능합니다. 만약 z := a and b; 와 같이 variable assign 한다 면 에러가 날 것입니다.

두 번째로 signal을 정의하고 이것을 초기 치로 설정할 수 있습니다. 사용 방법은 열거형 으로 정의하면 됩니다. 그러나 Assign의 방법이 조금 다릅니다.

signal temp : std\_logic\_vector(3 downto 0) := "1100";

세 번째로 일반적인 signal의 표현입니다. 저는 포트 시그널과 구별하기 위해서 이것을 내 부 signal이라는 표현을 사용합니다. (그러나 포트 시그널과 내부 시그널을 구별 없이 signal이라고 하는 것이 보통입니다.)

내부 시그널이라고 표현하는 이유는 a, b, c, d라는 입력이 있고 출력이 z라는 포트 선언이 있습니다. 그러나 a와 b를 더해서 e라는 값에 저장을 하고 c와 d를 더해서 f라는 값에 저장 을 합니다. e와 f를 더해서 z라는 값에 출력을 하는 회로가 있다고 합시다.

```

-- 필요 없는 부분은 삭제를 했습니다.

entity adder is

port ( a, b, c, d : in std_logic_vector(3 downto 0);

z : out std_logic_vector(3 downto 0));

end adder;

```

architecture temp of adder is

signal e : std\_logic\_vector(3 downto 0); signal f : std\_logic\_vector(3 downto 0);

begin

```

e <= a + b;

f <= c + d;

z <= e + f;

end temp;

```

위 부분에서 e와 f가 내부 시그널로 표현되었습니다. 그리고 Process 문에서도 사용 가능 합니다. 다만 그 시점에서 값이 바로 대입되지 않고 end process를 만나면 완료되어 값이 결정됩니다. 위의 예제는 그 시점에서 바로 값이 대입된다는 것을 알 수 있습니다. 왜 내부 시그널이라는 개념을 사용하는지 알겠습니까? 그리고 항상 내부 시그널은 architecture와 begin 사이에 들어가야 합니다. 이와 반대로 variable은 process 문안에 서만 사용할 수 있고 process 문과 begin 사이에 들어가야 합니다.

Variable은 process나 부프로그램(function과 procedure)에서만 사용되며 variable이 지니는 값도 process나 부프로그램 내에서만 유효한 내적 변수이다. variable은 signal과 같이 VHDL 합성 시에 바로 선으로 구현되는 것이 아니며, 중간 연산 단계에 주로 사용된다. variable에서 사용되는 assign 기호는 ':= '이고, 즉시(immediately)라는 의미를 가진다. signal과 비슷한 선언 방식을 사용한다.

```

-- 입력이 a와 b이고 출력이 c와 d일 때

variable tmp1, tmp2 : std_logic;

signal tmp3 : std_logic;

..

tmp1 := '1';

tmp2 := a and b;

..

c <= tmp1;

d \leq tmp2;

그 값을 돌려줄 때 signal <= variable; 라는 방식을 사용한다.

다음 예제는 3입력 and 게이트의 구현이다. 좀 차이점을 실감할 수 있을 것이다.

ex1) 3입력 and gate

library ieee;

use ieee. std_logic_1164.all;

entity and_3 is

port (a, b, c : in bit;

Ζ

: out bit);

end and_3;

architecture temp of and_3 is

begin

process(a, b, c)

variable temp : bit;

begin

temp := '1';

temp := a and temp;

temp := b and temp;

temp := c and temp;

z \leq temp;

end process;

end temp;

```

architecture 내에 process와 begin 사이에 variable temp를 선언하며, temp는 중간 단계의 연산 결과를 잠시 보관한다. 그러나 시그널처럼 즉시 그 값을 temp에 기록하지는 않는다. 이것이 signal과 variable의 미세한 차이이다. 다음 예제를 가지고 그 결과 값을 확인해 보 기를 바란다. signal로 표현한 3입력 and 게이트이다. 분명히 에러 또는 warning을 보게 될 것이다.

```

ex2)

library ieee;

use ieee. std_logic_1164.all;

entity and_3_1 is

port ( a, b, c : in bit;

: out bit);

Ζ

end and_3_1;

architecture temp of and_3_1 is

signal temp : bit;

begin

process(a, b, c)

begin

temp <= '1';

temp \leq = a and temp;

temp \leq b and temp;

temp \leq = c and temp;

z \leq temp;

end process;

end temp;

```

이 두 예제의 차이점을 이해했다면 어느 정도 signal과 variable의 차이점을 이해할 수 있 을 것이다.

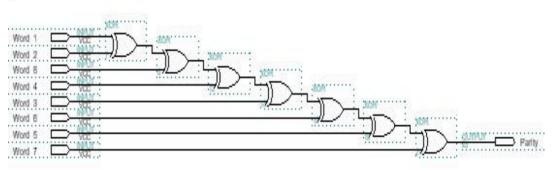

다음 예제를 구별할 수 있다면 충분히 다음으로 넘어갈 수 있을 것입니다. 이번 예제는 8 비트 Parity 체크 회로입니다. 패러티를 검사하는 회로에서 signal과 variable로 정의되었을 때와 다른 회로도를 보입니다. 그 차이점을 충분히 이해할 수 있었으면 하는 바람입니다. 그리고 for loop 구문이 사용됩니다. 어떻게 사용되는지 자세히 보고 다음에 활용해 보세 요.

```

ex3) 정상적인 Parity 체크 회로

library ieee;

use ieee. std_logic_1164.all;

entity parity is

port ( word : in bit_vector(7 downto 0);

parity : out bit);

end parity;

architecture rtl of parity is

begin

process

variable result : bit;

begin

result := '0';

for i in 0 to 7 loop

result := result xor word(i);

end loop;

parity <= result;

end process;

end rtl;

```

for loop 문은 별로 어려움 없이 이해할 수 있을 것입니다. 범위 시작에서 범위 끝까지 증 가하면서 수행하게 된다.

for 변수 in 범위 시작 to 범위끝 loop statement;

end loop;

13

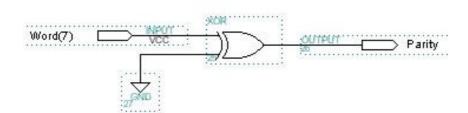

ex4)

library ieee;

use ieee. std\_logic\_1164.all;

entity parity is

port ( word : in bit\_vector(7 downto 0);

parity : out bit);

end parity;

architecture rtl of parity is

signal result : bit;

begin process

> begin result <= '0';

> > for i in 0 to 7 loop

> >  result <= result xor word(i);

> > end loop;</pre>

parity <= result; end process; end rtl;

Counter(Up/Down, Ring, Johnson, Gray Counter)

순차 회로의 대표적인 경우는 Counter가 있습니다. 계수기(Counter)가 무엇인지는 알겠지요. Clock의 입력을 받아 하나씩 증가하든지 감소하는 기능을 가진 회로를 말합니다. 간단한 기능을 가지고 있지만 대단히 활용 범위가 넓습니다. 카운터를 잘 활용하면 나중에 전자시계가 간단하게 설계할 수 있을 것입니다. 몇 비트든 상관없이 마음대로 설계할 수 있 을 것입니다.

```

ex1)

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_signed. all;

```

```

architecture rtl of upcount is

signal tmp : std_logic_vector(5 downto 0);

begin

count_out <= tmp;

process(clk, reset)

begin

if (reset='1') then

tmp <= "000000";

elsif (clk='1' and clk' event) then

tmp <= tmp + '1';

end if;

end process;

end rtl;</pre>

```

```

우선 내부 시그널의 위치를 살펴봅시다. architecture와 begin 사이에 들어갑니다. 그리고

모든 회로는 Concurrent하게 동작한다고 했죠. 그러니 count_out <= tmp; 와 Process 문

과는 두 개의 구문이 concurrent하게 동작합니다. Process 구문에서 마지막으로 tmp의 값이

결정되어 나옵니다. 그러면 count_out의 값이 결정됩니다.

process 내의 내용을 조금 살펴봅시다. reset이 1이라면 tmp의 값이 000000으로 결정됩니

다. elsif 구문에서 reset이 0이고, 클럭이 상승에지에서 1 증가된 값을 가지게 됩니다.

그리고 if 구문에 대해서 알아봅시다. if 구문이 사용된 예제는 앞에서 많이 보았죠.

if ... then

.... ,

end if;

위의 경우는 플립플롭의 경우라면 레치가 될 가능성이 많군요. 약간 불안정한 형태입니다.

if ... then .... ;

else

....

;

end if;

가장 대표적인 형태의 if 구문입니다.

```

```

if ... then .... ;

```

```

elsif .... ;

end if;

위의 예제의 경우가 사용된 형태입니다.

if ... then .... ;

elsif

....

;

....

else

....

;

end if;

조금 복잡한 형태의 구문입니다.

ex2)

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_signed. all;

entity upcount2 is

port ( clk, reset, enable, load : in std_logic;

: in std_logic_vector(5 downto 0);

databus

count_out : out std_logic_vector(5 downto 0));

end upcount2;

architecture rtl of upcount2 is

signal tmp : std_logic_vector(5 downto 0);

signal clkenable : std_logic;

begin

count_out <= tmp;</pre>

clkenable \leq clk and enable;

process(clkenable, reset, load)

begin

if (reset='1') then

tmp <= "000000";

elsif (clkenable='1' and clkenable' event) then

if (load='1') then

tmp <= databus;</pre>

else

tmp <= tmp + '1';

end if;

end if;

end process;

end rtl;

```

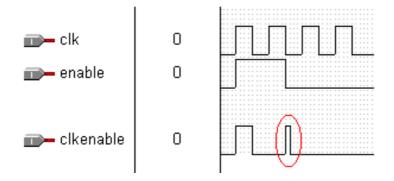

load가 1이면 databus의 값을 로드하게 되어 있군요. 약간 복잡하게 보입니다만 그렇게 복 잡한 형태는 아닙니다. 다만 clkenable라는 이상한 신호를 발견했을 것입니다.

**clkenable** <= **clk and enable**; 클럭 신호와 enable 신호의 and를 한 것이 clkenable 신호 입니다. 전문적인 용어로 **gated clock**이라고 합니다. 이 신호를 사용할 때는 Timing을 고 려해야 합니다. 그렇지 않으면 glitch가 발생할 가능성이 너무 많습니다.

그럼 왜 gated clock을 사용할까요. Synchronous 회로의 단점은 무엇일까요. 아마도 파워 소모가 너무 많다는 것입니다.

다음 Asynchronous 회로를 살펴봅시다.

clkenable은 전력 소모가 적지만 위의 그림과 같은 timing 문제를 반드시 고려해야 합니다. 그렇지 않으면 위의 그림과 같은 glitch가 발생하게 될 것입니다.

예제2의 경우 별로 설명할 것이 없네요. if 구문 속에 또 다른 if 구문이 들어갈 수 있다는 것에 대해서는 유심히 보세요. if 구문 속에 들어갈 수 있는 if 문의 제한은 없습니다. 그렇 지만 자기가 그것을 구별하는 데는 문제가 있을 것입니다. 그러니 적당한 탭을 사용하는 것 이 좋을 것이라 생각됩니다. 보기에도 깔끔하고 구분하기도 쉽게 말이죠.

```

ex3)

library ieee;